# электроники

К. Фрике

Вводный курс цифровой электроники

Перевод с немецкого под ред. Н.Л. Бирюкова

ТЕХНОСФЕРА Москва 2021

УДК 621.38 ББК 32.85 Ф88

#### Ф88 Фрике К.

Вводный курс цифровой электроники

Москва: ТЕХНОСФЕРА, 2021. - 396 с. ISBN 978-5-94836-616-6

В книге подробно изложены основы цифровой техники, включая устройство и программирование простых микропроцессоров. Помимо прочной теоретической базы, читатель получит знания, позволяющие понять принципы работы большинства цифровых схем.

В новое 8-е издание внесены многочисленные изменения и дополнения, касающиеся актуальных на сегодняшних день направлений развития цифровой техники. В частности, большое внимание уделено технологии программируемых пользователем схем (ASIC/ПЛИС) и их конфигурации с помощью языка HDL, представлены структура и программирование микропроцессоров с помощью ассемблера. В качестве примера подробно рассматривается популярный современный микроконтроллер ATmega16.

Книга предназначена в первую очередь для студентов профильных вузов, а также для широкого круга радиолюбителей и других заинтересованных читателей. Излагаемый материал хорошо структурирован, сопровождается многочисленными примерами, а также упражнениями с решениями, что позволит успешно применять данную книгу как в учебном процессе, так и для самостоятельного изучения рассматриваемых вопросов и применения их на практике.

УДК 621.38 ББК 32.85

First published in German under the title Digitaltechnik; Lehr- und Übungsbuch für Elektrotechniker und Informatiker by Klaus Fricke, edition: 8 Copyright © Springer Fachmedien Wiesbaden GmbH, ein Teil von Springer Nature 1999, 2001, 2002, 2005, 2007, 2009, 2014, 2018

This edition has been translated and published under licence from

Springer Fachmedien Wiesbaden GmbH, part of Springer Nature.

Springer Fachmedien Wiesbaden GmbH, part of Springer Nature takes no responsibility

and shall not be made liable for the accuracy of the translation.

©АО «РИЦ «ТЕХНОСФЕРА», перевод на русский язык, оригинал-макет, оформление, 2021

ISBN 978-5-94836-616-6 ISBN 978-3-658-21065-6 (Hem.)

### СОДЕРЖАНИЕ

| ПРЕД                | исловие                                                          | ,11  |

|---------------------|------------------------------------------------------------------|------|

|                     |                                                                  |      |

| ГЛАВ                | A 1.                                                             |      |

| ВВЕД                | ЕНИЕ                                                             | . 14 |

|                     |                                                                  |      |

|                     |                                                                  |      |

| ГЛАВ                | А 2.<br>ІРОВАНИЕ И СИСТЕМЫ СЧИСЛЕНИЯ                             | 17   |

| <b>коди</b><br>2.1. | Коды                                                             |      |

| 2.1.                | Двоичный код                                                     |      |

| 2.2.                | Арифметические операции с фиксированной                          | 10   |

| 2.3.                | запятой в двоичной системе                                       | 20   |

| 2.3.1.              | Целочисленное сложение в двоичной системе                        |      |

| 2.3.2.              | Сложение чисел с фиксированной запятой                           |      |

| 2.3.3.              | Представление с помощью обратного кода                           |      |

| 2.3.4.              | Представление с помощью двойного дополнения                      |      |

|                     | (точное дополнение, two's complement)                            | . 22 |

| 2.3.5.              | Вычитание при представлении с помощью                            |      |

|                     | точного дополнения                                               |      |

| 2.3.6.              | Переполнение числового диапазона                                 |      |

| 2.3.7.              | Умножение                                                        |      |

| 2.3.8.              | Деление                                                          |      |

| 2.4.                | Представление вещественных чисел с плавающей запятой             | 26   |

| 2.4.1.              | Введение: представление с плавающей запятой                      | 26   |

| 2.4.2               | в десятичной системе счисления                                   | . 26 |

| 2.4.2.              | Представление с плавающей запятой в двоичной системе счисления   | 27   |

| 2.4.3.              | Особые представления чисел                                       |      |

| 2.4.3.              | Осооые представления чисел — — — — — — — — — — — — — — — — — — — |      |

| 2.6.                | Восьмеричный код                                                 |      |

| 2.7.                | Код Грея                                                         |      |

| 2.7.                | Двоично-десятичный код                                           |      |

| 2.8.                |                                                                  |      |

|                     | Алфавитно-цифровые коды                                          |      |

| 2.10.               | Упражнения                                                       | 33   |

|                     |                                                                  |      |

| ГЛАВ                | A 3.                                                             |      |

|                     |                                                                  | .35  |

| 3.1.                | Переключательная переменная и переключательная функция           |      |

| 3.2.                | Двухразрядные переключательные функции                           |      |

| · · ·               | <del></del>                                                      |      |

| 3.3.   | Вычислительные правила                                    | 40 |

|--------|-----------------------------------------------------------|----|

| 3.4.   | Упрощенное обозначение                                    |    |

| 3.5.   | Каноническая дизъюнктивная нормальная форма (KDNF)        | 41 |

| 3.6.   | Каноническая конъюнктивная нормальная форма (KKNF)        |    |

| 3.7.   | Представление функций с помощью KKNF и KDNF               |    |

| 3.8.   | Минимизация с помощью переключательной алгебры            | 46 |

| 3.9.   | Символическое обозначение логических элементов            |    |

| 3.9.1. | Основы структуры символов                                 |    |

| 3.9.2. | Индексация зависимости                                    |    |

| 3.9.3. | Зависимость вида И (G)                                    |    |

| 3.9.4. | Зависимость по типу ИЛИ (V)                               | 50 |

| 3.9.5. | Зависимость по типу EXOR (N)                              | 50 |

| 3.9.6. | Образующая соединение зависимость (Z)                     | 51 |

| 3.9.7. | Зависимость с передачей (Х)                               | 51 |

| 3.10.  | Упражнения                                                | 52 |

|        |                                                           |    |

|        |                                                           |    |

| ГЛАВ   |                                                           |    |

| ПРИІ   | НЦИПЫ РАБОТЫ ЛОГИЧЕСКИХ ВЕНТИЛЕЙ                          |    |

| 4.1.   | Положительная и отрицательная логика                      | 55 |

| 4.2.   | Определение времени переключения                          | 56 |

| 4.3.   | Передаточная характеристика, запас по помехоустойчивости. | 57 |

| 4.4.   | Вентили                                                   | 60 |

| 4.4.1. | Вентили с открытым коллектором (open collector)           | 61 |

| 4.4.2. | Вентиль с тремя состояниями                               | 62 |

| 4.5.   | Упражнения                                                | 63 |

|        |                                                           |    |

|        |                                                           |    |

| ГЛАВ   | A 5.                                                      |    |

| CXEN   | ИОТЕХНИКА                                                 |    |

| 5.1.   | КМОП                                                      | 65 |

| 5.1.1. |                                                           |    |

| 5.1.2. | Основные схемы NAND и NOR                                 |    |

| 5.1.3. | Передаточный вентиль                                      |    |

| 5.1.4. | Элемент с тремя состояниями                               |    |

| 5.1.5. | Специфические свойства КМОП                               | 71 |

| 5.2.   | ТТЛ                                                       |    |

| 5.2.1. | Нагрузка выходов                                          |    |

| 5.3.   | Эмиттерно-связанная логика                                | 76 |

| 5.4.   | Интегральная инжекционная логика (I2L)                    | 77 |

| 5.5.   | Рассеиваемая мощность и характеристики переключения       |    |

|        | транзисторных переключателей                              | 78 |

| 5.6.   | Упражнения                                                | 80 |

|        |                                                           |    |

| ГЛАВ   | A 6.                                                         |     |

|--------|--------------------------------------------------------------|-----|

| ЛОГИ   | ІЧЕСКИЕ СХЕМЫ                                                | 82  |

| 6.1.   | Минимизация с помощью диаграмм Карно – Вейча                 | 82  |

| 6.1.1. | Минимизация KDNF                                             |     |

| 6.1.2. | Минимизация нормальной KKNF                                  |     |

| 6.1.3. | Диаграммы Карно – Вейча для 2, 3, 4, 5, 6 входных переменных | 87  |

| 6.1.4. | Неполностью заданные функции                                 | 88  |

| 6.2.   | Способ Квина – Мак-Класки                                    |     |

| 6.3.   | Другие направления оптимизации                               |     |

| 6.3.1. | Преобразование логической схемы И/ИЛИ в схему НЕ-И           |     |

| 6.3.2. | Преобразование логической схемы ИЛИ/И в логическую           |     |

|        | схему НЕ-ИЛИ                                                 | 95  |

| 6.4.   | Воздействие времени задержки на логические схемы             | 95  |

| 6.4.1. | Отрицательное воздействие на структуру                       |     |

| 6.4.2. | Отрицательное воздействие на функционирование                |     |

| 6.4.3. | Классификация отрицательных воздействий                      | 98  |

| 6.5.   | Упражнения                                                   | 98  |

|        | •                                                            |     |

|        |                                                              |     |

| ГЛАВ   | A 7.                                                         |     |

| АСИН   | ІХРОННЫЕ СХЕМЫ ПЕРЕКЛЮЧЕНИЯ                                  | 101 |

| 7.1.   | Принципиальные особенности структуры триггеров               | 102 |

| 7.2.   | Анализ асинхронных триггеров                                 |     |

| 7.3.   | Систематический анализ                                       |     |

| 7.4.   | Анализ с учетом задержки вентилей                            |     |

| 7.5.   | Элементы ЗУ                                                  |     |

| 7.5.1. | RS-триггер                                                   |     |

| 7.5.2. | RS-триггер с тактовым входом                                 |     |

| 7.5.3. | D-триггер                                                    |     |

| 7.5.4. | D-триггер с управлением по переднему фронту импульса         |     |

| 7.5.5. | Управление по двум фронтам                                   |     |

| 7.5.6. | ЈК-триггер                                                   | 118 |

| 7.5.7. | Т-триггер                                                    | 120 |

| 7.5.8. | Пример                                                       | 120 |

| 7.5.9. | Обобщенные сведения о триггерах                              | 121 |

| 7.6.   | Упражнения                                                   | 123 |

|        |                                                              |     |

|        |                                                              |     |

| ГЛАВ   | A 8.                                                         |     |

| СИНХ   | КРОННЫЕ ДРАЙВЕРЫ                                             | 126 |

| 8.1.   | Пример 1: «Двоичный счетчик»                                 |     |

| 8.2.   | Переключатель Мура                                           |     |

| 8.3.   | Схема Мили                                                   |     |

| 8.3.1. |                                                              |     |

| 8.3.2.           | Реализация управления машиной в виде                           |     |

|------------------|----------------------------------------------------------------|-----|

|                  | распределительного устройства Мура                             | 135 |

| 8.4.             | Кодирование состояний                                          | 136 |

| 8.4.1.           | Двоичное кодирование                                           | 137 |

| 8.4.2.           | Кодирование по коду Грея                                       | 137 |

| 8.4.3.           | Кодирование, ориентированное на вывод                          | 137 |

| 8.4.4.           | «Горячее» кодирование                                          | 141 |

| 8.5.             | Выбор триггеров                                                |     |

| 8.6.             | Временные характеристики схем переключения                     |     |

| 8.7.             | Упражнения                                                     |     |

|                  | <b>-</b>                                                       |     |

| ГЛАВ             |                                                                | 150 |

|                  | ЬТИПЛЕКСОРЫ И ПРЕОБРАЗОВАТЕЛИ КОДА                             |     |

| 9.1.             | Мультиплексор                                                  |     |

| 9.1.1.           | Реализация функций мультиплексора                              |     |

| 9.2.             | Преобразователь кода                                           | 154 |

| 9.2.1.           | Преобразователь двоично-десятичного кода в десятичный код 7442 | 155 |

| 9.2.2.           |                                                                |     |

| 9.2.2.           | Демультиплексор                                                |     |

|                  | Генерирование наборов функций                                  |     |

| 9.3.             | Аналоговые мультиплексоры и демультиплексоры                   |     |

| 9.4.             | Упражнения                                                     | 160 |

| ГЛАВ             | A 10                                                           |     |

|                  | А 10.<br>РОВЫЕ СЧЕТЧИКИ                                        | 163 |

| ,                | Асинхронный счетчик                                            |     |

|                  | Двоичный счетчик по модулю 8                                   |     |

|                  | Счетчик по модулю 6                                            |     |

|                  | Асинхронный обратный счетчик                                   |     |

|                  | Временные характеристики асинхронных счетчиков                 |     |

|                  | Синхронные счетчики                                            |     |

|                  | 4-битовый двоичный счетчик                                     |     |

|                  | Счетчик по модулю 6 с использованием кода Грея                 |     |

|                  | Синхронный 4-битовый реверсивный двоичный счетчик 74191        |     |

| 10.3.            | Упражнения                                                     |     |

| 10.0.            | • 1.punii • 1.10                                               | 175 |

| ГЛАВ             | A 11.                                                          |     |

|                  | ІСТРЫ СДВИГА                                                   | 175 |

| 11.1.            | Временные характеристики регистров сдвига                      |     |

|                  | Регистр сдвига на микросхеме 74194                             |     |

| 11.2.            |                                                                |     |

| · <del>- ·</del> | • • • • parrior • brisbre                                      |     |

| 11.2.1.                                                                                                                                                   | Счетчик Мебиуса, счетчик Джонсона                                                                                                                                                                                                                                                                                | 181                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 11.2.2.                                                                                                                                                   | Псевдослучайные последовательности                                                                                                                                                                                                                                                                               | 183                                                                              |

| 11.3.                                                                                                                                                     | Упражнения                                                                                                                                                                                                                                                                                                       | 185                                                                              |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| ГЛАВА                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                                                                                                                                           | РМЕТИЧЕСКИЕ УСТРОЙСТВА                                                                                                                                                                                                                                                                                           |                                                                                  |

| 12.1.                                                                                                                                                     | Полный сумматор                                                                                                                                                                                                                                                                                                  |                                                                                  |

| 12.2.                                                                                                                                                     | Последовательный сумматор                                                                                                                                                                                                                                                                                        |                                                                                  |

| 12.3.                                                                                                                                                     | Сумматор с последовательным переносом (ripple-carry-adder)                                                                                                                                                                                                                                                       |                                                                                  |

| 12.4.                                                                                                                                                     | Сумматор с параллельным переносом                                                                                                                                                                                                                                                                                |                                                                                  |

|                                                                                                                                                           | Каскадирование сумматоров с параллельным переносом                                                                                                                                                                                                                                                               |                                                                                  |

|                                                                                                                                                           | Сравнение сумматоров                                                                                                                                                                                                                                                                                             | 196                                                                              |

| 12.5.                                                                                                                                                     | Арифметико-логические вычислительные                                                                                                                                                                                                                                                                             |                                                                                  |

|                                                                                                                                                           | устройства (ALU, АЛУ)                                                                                                                                                                                                                                                                                            |                                                                                  |

|                                                                                                                                                           | Примеры операций                                                                                                                                                                                                                                                                                                 |                                                                                  |

|                                                                                                                                                           | Компараторы                                                                                                                                                                                                                                                                                                      |                                                                                  |

|                                                                                                                                                           | 2-битовый компаратор                                                                                                                                                                                                                                                                                             |                                                                                  |

|                                                                                                                                                           | Каскадируемые компараторы                                                                                                                                                                                                                                                                                        |                                                                                  |

| 12.7.                                                                                                                                                     | Упражнения                                                                                                                                                                                                                                                                                                       | 203                                                                              |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                  |                                                                                  |

| THAD.                                                                                                                                                     | A 12                                                                                                                                                                                                                                                                                                             |                                                                                  |

| ГЛАВА                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                  | 204                                                                              |

| ЦИФ                                                                                                                                                       | РОВЫЕ ЗУ                                                                                                                                                                                                                                                                                                         |                                                                                  |

| <b>ЦИФ</b> 113.1.                                                                                                                                         | РОВЫЕ ЗУПринципиальная структурная схема ЗУ                                                                                                                                                                                                                                                                      | 205                                                                              |

| ЦИФ<br>13.1.<br>13.2.                                                                                                                                     | РОВЫЕ ЗУПринципиальная структурная схема ЗУROM                                                                                                                                                                                                                                                                   | 205<br>206                                                                       |

| <b>ЦИФ</b> 1<br>13.1.<br>13.2.<br>13.3.                                                                                                                   | РОВЫЕ ЗУПринципиальная структурная схема ЗУROMPROM                                                                                                                                                                                                                                                               | 205<br>206<br>209                                                                |

| ЦИФ<br>13.1.<br>13.2.<br>13.3.<br>13.4.                                                                                                                   | РОВЫЕ ЗУПринципиальная структурная схема ЗУROMPROMPROM                                                                                                                                                                                                                                                           | 205<br>206<br>209<br>209                                                         |

| ЦИФ)<br>13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.                                                                                                         | POBЫE ЗУ Принципиальная структурная схема ЗУ ROM PROM EPROM EEPROM                                                                                                                                                                                                                                               | 205<br>206<br>209<br>211                                                         |

| ЦИФ<br>13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.                                                                                                 | POBЫE ЗУ Принципиальная структурная схема ЗУ ROM PROM EPROM EEPROM EAROM                                                                                                                                                                                                                                         | 205<br>206<br>209<br>209<br>211<br>211                                           |

| ЦИФ<br>13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.                                                                                        | POBЫE ЗУ                                                                                                                                                                                                                                                                                                         | 205<br>206<br>209<br>209<br>211<br>212                                           |

| ЦИФ<br>13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.                                                                               | POBЫE ЗУ Принципиальная структурная схема ЗУ ROM PROM EPROM EEPROM EAROM NOVRAM RAM                                                                                                                                                                                                                              | 205<br>206<br>209<br>209<br>211<br>212                                           |

| ЦИФ<br>13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.                                                                    | РОВЫЕ ЗУ                                                                                                                                                                                                                                                                                                         | 205<br>206<br>209<br>211<br>211<br>212<br>212                                    |

| ЦИФ<br>13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.<br>13.8.2.                                                         | РОВЫЕ ЗУ         Принципиальная структурная схема ЗУ         ROM         PROM         EPROM         EEPROM         EAROM         NOVRAM         RAM         Статическое RAM         Пример работы RAM                                                                                                            | 205<br>206<br>209<br>211<br>211<br>212<br>212<br>213                             |

| ЦИФ<br>13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.<br>13.8.2.<br>13.9.                                                | РОВЫЕ ЗУ         Принципиальная структурная схема ЗУ         ROM         PROM         EPROM         EEPROM         EAROM         NOVRAM         RAM         Статическое RAM         Пример работы RAM         Динамическое RAM (DRAM)                                                                            | 205<br>206<br>209<br>211<br>211<br>212<br>213<br>213                             |

| ЦИФ<br>13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.<br>13.8.2.<br>13.9.<br>13.9.1.                                     | РОВЫЕ ЗУ         Принципиальная структурная схема ЗУ         ROM         PROM         EPROM         EAROM         NOVRAM         RAM         Статическое RAM         Пример работы RAM         Динамическое RAM (DRAM)         Структура DRAM                                                                    | 205<br>206<br>209<br>211<br>211<br>212<br>213<br>213<br>217                      |

| 13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.<br>13.8.2.<br>13.9.<br>13.9.1.                                            | РОВЫЕ ЗУ         Принципиальная структурная схема ЗУ         ROM         PROM         EPROM         EAROM         NOVRAM         RAM         Статическое RAM         Пример работы RAM         Динамическое RAM (DRAM)         Структура DRAM         Пример DRAM                                                | 205<br>206<br>209<br>211<br>211<br>212<br>213<br>213<br>217                      |

| 13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.<br>13.8.2.<br>13.9.<br>13.9.1.<br>13.9.2.<br>13.10.                       | РОВЫЕ ЗУ         Принципиальная структурная схема ЗУ         ROM         PROM         EPROM         EEPROM         EAROM         NOVRAM         RAM         Статическое RAM         Пример работы RAM         Динамическое RAM (DRAM)         Структура DRAM         Пример DRAM         SDRAM (синхронная DRAM) | 205<br>206<br>209<br>211<br>211<br>212<br>213<br>213<br>217<br>218               |

| 13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.<br>13.8.2.<br>13.9.<br>13.9.1.<br>13.9.2.<br>13.10.                       | РОВЫЕ ЗУ         Принципиальная структурная схема ЗУ         ROM         PROM         EPROM         EAROM         NOVRAM         RAM         Статическое RAM         Пример работы RAM         Динамическое RAM (DRAM)         Структура DRAM         Пример DRAM                                                | 205<br>206<br>209<br>211<br>211<br>212<br>213<br>213<br>217<br>218               |

| 13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.<br>13.8.2.<br>13.9.<br>13.9.1.<br>13.9.2.<br>13.10.                       | РОВЫЕ ЗУ         Принципиальная структурная схема ЗУ         ROM         PROM         EPROM         EEPROM         EAROM         NOVRAM         RAM         Статическое RAM         Пример работы RAM         Динамическое RAM (DRAM)         Структура DRAM         Пример DRAM         SDRAM (синхронная DRAM) | 205<br>206<br>209<br>211<br>211<br>212<br>213<br>217<br>217<br>218<br>222        |

| 13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.<br>13.8.2.<br>13.9.<br>13.9.1.<br>13.9.2.<br>13.10.<br>13.11.             | РОВЫЕ ЗУ                                                                                                                                                                                                                                                                                                         | 205<br>206<br>209<br>211<br>212<br>212<br>213<br>217<br>217<br>218<br>222<br>223 |

| 13.1.<br>13.2.<br>13.3.<br>13.4.<br>13.5.<br>13.6.<br>13.7.<br>13.8.<br>13.8.1.<br>13.8.2.<br>13.9.1.<br>13.9.2.<br>13.10.<br>13.11.<br>13.12.<br>13.12.1 | РОВЫЕ ЗУ                                                                                                                                                                                                                                                                                                         | 205 206 209 209 211 211 212 213 217217218 222 223 223                            |

| 13.15.         | Увеличение емкости ЗУ                             | . 227 |

|----------------|---------------------------------------------------|-------|

|                | I. Полное декодирование                           |       |

| 13.15.2        | 2. Частичное декодирование                        | 229   |

| 13.15.3        | 3. Линейное декодирование                         | 231   |

| 13.16.         | Упражнения                                        | 233   |

|                |                                                   |       |

|                |                                                   |       |

| ГЛАВ           | A 14.                                             |       |

| ПРОІ           | ГРАММИРУЕМЫЕ ЛОГИЧЕСКИЕ МАТРИЦЫ – ПЛМ             | . 235 |

| 14.1.          | Семейства ASIC                                    | 236   |

| 14.2.          | ПЛИС (PLD)                                        | 240   |

| 14.2.1.        | Типы PLD – ПЛИС                                   |       |

| 14.3.          | ROM, EPROM, EEPROM                                | 242   |

| 14.4.          | PLA                                               |       |

| 14.5.          | PAL                                               |       |

| 14.6.          | GAL                                               |       |

| 14.7.          | Программирование ПЛИС (PLD)                       |       |

|                | Тестирование                                      |       |

| 14.8.          | •                                                 |       |

|                | Структура FPGA                                    |       |

|                | Конфигурируемые логические блоки (СLВ)            |       |

|                | ІО-блоки                                          |       |

|                | Соединительные линии                              |       |

|                | Программирование FPGA                             |       |

|                | CPLD                                              |       |

|                | Структура CPLD                                    |       |

|                | Блоки логических массивов (LAB)                   |       |

| 14.9.3.        | ІО-контроль                                       | 267   |

| 14.9.4.        | Размер CPLD                                       | 268   |

| 14.10.         | Вентильные матрицы                                | 268   |

|                | 1. Структура канализированных вентильных матриц   |       |

|                | ASIC со стандартными ячейками                     |       |

|                | ASIC на основе полностью заказного проектирования |       |

|                | Упражнения                                        |       |

| 1              | v iipumiiviiii)                                   | _, .  |

|                |                                                   |       |

| ГЛАВ           | A 15.                                             |       |

|                | К ПРОЕКТИРОВАНИЯ VHDL                             | 276   |

| 15.1.          | Методы проектирования цифровых схем               |       |

| 15.1.          | Структура VHDL                                    |       |

| 15.2.          | Типы                                              |       |

| 15.3.<br>15.4. |                                                   |       |

|                | Операторы                                         |       |

| 15.5.          | Объект                                            |       |

| 15.6.          | Архитектура                                       | . 283 |

| 15.7.   | Процессы                                      | 285 |

|---------|-----------------------------------------------|-----|

| 15.8.   | Структурное проектирование                    | 290 |

| 15.9.   | Шины                                          |     |

| 15.10.  | Упражнения                                    |     |

| 101101  | •                                             | , . |

|         |                                               |     |

| ГЛАВА   | A 16.                                         |     |

|         | РОПРОЦЕССОРЫ                                  | 295 |

| 16.1.   | ·                                             |     |

| 16.2.   |                                               |     |

|         | Операционный блок                             |     |

|         | Управляющее устройство                        |     |

|         | Запоминающее устройство (память)              |     |

|         | Устройства ввода-вывода                       |     |

|         | Режим работы                                  |     |

| 16.3.   | -                                             |     |

|         | Выводы микросхемы ATmega16                    |     |

|         | Регистры центрального процессора              |     |

|         | Программная память                            |     |

|         | ЗУ для хранения данных                        |     |

|         | Процедуры выполнения команд                   |     |

|         | Программирование на ассемблере                |     |

|         |                                               |     |

|         | Типы адресации                                |     |

| 16.6.   |                                               |     |

|         | Соглашения                                    |     |

|         | Команда перемещения                           |     |

| 16.6.3. | F,                                            |     |

|         | Запись байтов                                 |     |

|         | Арифметические операции: Отрицание            |     |

|         | Арифметические операции: сложение и вычитание | 321 |

| 10.0.7. | в регистре                                    | 224 |

| 1660    | Арифметические команды: проверка и сравнение  |     |

|         | Арифметические команды: проверка и сравнение  |     |

|         | . Команды сдвига и ротации                    |     |

|         | . Команды сдвига и рогации                    |     |

|         | . Безусловный адресный переход                |     |

|         | Относительный переход по адресу               |     |

|         | . Условно адресуемые команды перехода         |     |

|         | . Команды перехода                            |     |

|         | . Команды подпрограмм                         |     |

| 16.7.   |                                               |     |

|         | Инструкции на языке ассемблера                |     |

| 16.8.   | Обработка прерываний                          |     |

| 16.9.   | Задания                                       | 343 |

## Содержание

#### приложения

| А.1. Обозначения функций                    | 344 |

|---------------------------------------------|-----|

| А.2. Набор команд микроконтроллера ATmega16 | 348 |

| А.3. Решения задач                          | 353 |

| А.4. Литература                             |     |

| А.5. Предметный указатель                   |     |

#### ПРЕДИСЛОВИЕ

Сегодня знание цифровой техники требуется в очень многих областях. Невозможно понять принципы работы мобильной связи, микрокомпьютерных технологий, систем цифрового управления и различного телекоммуникационного оборудования без знания методов цифровой обработки информации, а широкое применение интегрированных механико-электронных систем лишь усиливает эту тенденцию. Особое значение цифровые технологии приобрели во встраиваемых системах. Речь идет о цифровых схемах, которые «встраиваются» в те или иные технические решения. Встраиваемые системы вы можете встретить в самых разных устройствах — стиральных машинах, автомобилях, холодильниках, развлекательной электронике, мобильных телефонах и т. д.

В данной книге отлично изложены основы цифровой техники, включая устройство и программирование простых микропроцессоров. Помимо прочной теоретической базы, читатель получит знания, позволяющие понять принципы работы большинства цифровых схем. В это 8-е издание внесены многочисленные дополнения. В частности, в главе о микропроцессорах в качестве примера рассматривается микропроцессор, широко используемый в современной промышленности. Также добавлен материал о представлении чисел с плавающей запятой.

Эта книга предназначена, в первую очередь, для студентов колледжей и университетов, изучающих инженерию и информационные технологии. Поскольку для понимания книги не требуется никаких специальных знаний, она также подходит для широкого круга заинтересованных читателей. Для работы с главой «Схемотехника» читателю понадобятся базовые знания в области электроники, однако эта глава не обязательна для понимания других глав книги, и ее можно пропустить. Представление булевой алгебры и используемые символы в основном соответствуют действующим стандартам DIN<sup>1</sup>.

DIN (Deutsches Institut für Normung) — Немецкий институт по стандартизации — Примеч. науч. ред.

Для облегчения самостоятельной работы с книгой каждая глава сопровождается упражнениями, с помощью которых можно проверить понимание материала. Предлагаемые решения можно найти в приложении. Одна из основных задач данной книги — это подробное изложение основ цифровой техники. В частности, много внимания уделено синтезу коммутационных схем. Рассмотрены примеры широко применяемых стандартных коммутационных схем, таких как мультиплексоры и преобразователи кола. Поскольку для понимания работы процессоров важно знание арифметических операций, подробно рассматриваются арифметика с фиксированной запятой и аппаратная реализация арифметико-логических устройств. Сегодня в распоряжении разработчиков схем находятся совершенные инструменты проектирования, позволяющие разрабатывать сложные цифровые схемы, реализовывать их на основе полупроводников, тестировать и настраивать работу схемы. Это обусловило бурное развитие интегральных схем специального назначения (ASIC), которые заказчик может настроить самостоятельно. Поэтому одна из глав посвящена таким интегральным схемам. Следующая глава знакомит с VHDL – языком программирования для описания, синтеза и моделирования интегральных цифровых схем, который фактически стал стандартом и часто используется при проектировании схем ASIC. Такой язык описания оборудования (HDL) становится все более популярным при проектировании схем, поскольку он дает значительные преимущества по сравнению с традиционными методами графически ориентированного проектирования, особенно при работе над сложными проектами. Опираясь на знание коммутационных схем, можно переходить к изучению синхронных и асинхронных методов коммутации. В книге представлена методика разработки синхронных и асинхронных контроллеров. При этом в новой редакции больше внимания уделено синхронным контроллерам. Методы асинхронной коммутации сейчас применяются, главным образом, в триггерах, наиболее распространенные типы которых представлены в книге. Кроме того, рассмотрено проектирование счетчиков и регистров сдвига и представлены некоторые примеры их промышленной реализации. Отдельная глава посвящена сравнению различных технологий и свойств модулей памяти, которые существенно влияют на характеристики современных вычислительных систем. Приведены типовые временные диаграммы, иллюстрирующие принципы работы различных модулей памяти. Последняя глава представляет простое введение в микропроцессорную технику. Для знакомства с устройством вычислительной машины поясняется принцип работы компьютера фон Неймана, на примере которого описываются процессы выполнения команд. В качестве практического примера в одном из разделов представлен современный микроконтроллер ATmega16 производства компании AVR, описаны его структура и режимы работы. Подробно рассматривается программирование на ассемблере, знание которого будет полезно при работе с различными типами процессоров.

Фульда, март 2018 года, Клаус Фрике

#### ГЛАВА І

#### **ВВЕДЕНИЕ**

В последние годы значение цифровой техники все более и более возрастает. Причина этого заключается в значительных преимуществах цифровой техники при создании очень сложных систем. Это достигается путем представления сигнала двумя значениями, которые могут обрабатываться логическими вентилями с сильно нелинейными передаточными характеристиками без сбоев, накопления и дальнейшего распространения искажений сигнала. Благодаря такому представлению сигналов удалось создать полупроводниковую технологию, позволяющую реализовать до  $10^7$  элементов на одном кристалле.

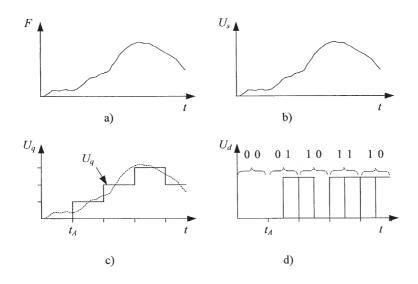

Поскольку целью систем цифровой техники является обработка сигналов, то следует несколько подробнее рассмотреть понятие «сигнал». Сигналы служат для переноса информации. Они описываются такими физическими величинами, как напряжение, ток, давление, сила и т. д. Амплитуды таких величин зависят от времени. Передаваемая информация заключается в изменяющихся амплитудных значениях. Пусть, например, измеряется зависящий от времени уровень жидкости F в резервуаре. На рис. 1.1а показана зависимость уровня жидкости от времени. Если датчик выдает электрический сигнал, напряжение которого пропорционально величине заполнения, получаем временную зависимость напряжения  $U_s$ , показанную на рис. 1.1 b. Этот сигнал имеет непрерывную величину, то есть в измеряемом диапазоне могут появиться все значения амплитуды.

Системы, которые могут обрабатывать непрерывные по величине сигналы, называются аналоговыми системами.

Дискретные по величине сигналы, которые также называют цифровыми сигналами, могут, в отличие от этого, принимать только определенные дискретные значения в фиксированные моменты времени. Примером цифрового сигнала является сигнал, который с помощью двух различных уровней напряжения показывает, закрыта или открыта дверь. Подобные сигналы могут непосредственно обрабатываться цифровыми системами.

В том случае, если сигналы с непрерывной величиной должны передаваться цифровыми системами, эти сигналы должны быть предварительно квантизированы. В соответствии с данным процессом, с определенными временными точками (точками считывания) соотнесена амплитуда сиг-

нала дискретной амплитудной ступени. Вышеупомянутый пример продемонстрирован на рис. 1.1с, показывающем датчик уровня заполнения. При этом получаем напряжение с дискретными величинами  $U_q$ . При квантизировании необходимо принимать во внимание ошибку округления.

Рис. 1.1. Пример «оцифровывания» сигналов.

- а) Зависимость от времени t уровня наполнения резервуара F.

- b) Зависимость от времени выходного напряжения датчика  $U_{\cdot}$ .

- с) Квантизированная зависимость от времени напряжения  $U_q$  при 4 амплитудных ступенях.

- d) Приведение амплитуд в соответствие с записью величин в виде кода  $00,\,01,\,10$  и 11

При цифровой передаче сигнал вначале должен быть переведен в цифровую форму. В этом случае амплитуда будет предъявляться с помощью последовательности цифр. Каждая цифра представляет собой сигнал с дискретным значением. На рис. 1.1d приведен пример кодирования с помощью нескольких следующих друг за другом цифр. Амплитудная ступень 0 представлена двумя цифрами 00. Амплитуды 1, 2 и 3 становятся сочетаниями 01, 10, 11. Следует различать также дискретные во времени сигналы и непрерывные во времени сигналы. Дискретные во времени сигналы могут изменять свою амплитуду только в определенные моменты времени, в то время как непрерывные во времени сигналы могут изменять свою амплитуду в произвольные моменты времени. Цифровые системы могут быть дискретными во времени, в этом случае их называют синхронными. Синхронизация осуществляется с помощью тактового сигнала.

Благодаря ограничению в использовании конечного числа амплитудных ступеней, цифровая система обладает высокой помехозащищенностью. Подвергнувшиеся воздействию помех цифровые сигналы могут быть однозначно приведены к первоначальным дискретным амплитудным значениям. Но чтобы не возникла ошибка, помеха не должна превышать половину расстояния между двумя амплитудными ступенями.

Цифровые системы имеют ряд преимуществ перед аналоговыми системами:

- При использовании цифровых сигналов не происходит накопления их искажений появляется возможность реализации систем любой степени сложности, например микропроцессоров. Это свойство цифровых систем определяет их превосходство и при передаче на большие расстояния.

- Цифровые системы сравнительно легко проектировать, поскольку способ их описания, представляющий собой булеву алгебру, аппарат очень удобный для автоматизации. Сегодня разработка сложных цифровых систем автоматизирована посредством применения высокопроизводительных алгоритмов.

- Цифровые системы можно относительно просто тестировать.

#### Недостаток цифровых систем:

Цифровые системы являются более медленными системами, чем аналоговые. Поэтому в области высоких частот доминирует аналоговая техника.

#### ГЛАВА 2

## КОДИРОВАНИЕ И СИСТЕМЫ СЧИСЛЕНИЯ

#### 2.1. Коды

В цифровой технике коды используются для оптимального представления сигнала в случае его применения. Код отображает символы одного множества через символы второго множества. При этом должна существовать возможность декодирования, при которой вероятно получить исходные символы из кодированных.

Известным примером кода является код Морзе. Определение кода производится с помощью таблицы соответствия. Для кода Морзе подобное соответствие отображено в табл. 2.1. Этот код является обратимым, так как из буквы можно получить символ Морзе, а из него можно вновь образовать букву. Но это справедливо только для текста, написанного строчными буквами, поскольку код Морзе не делает различия между прописными и строчными буквами. Строго говоря, из кода Морзе нельзя восстановить путем декодирования текст, записанный с помощью строчных и прописных букв.

Таблица 2.1. Код Морзе

| Алфавит | Код Морзе | Алфавит | Код Морзе | Алфавит | Код Морзе |

|---------|-----------|---------|-----------|---------|-----------|

| a       | •-        | j       | ·         | S       | • • •     |

| b       | . – . –   | k       | - · -     | t       | _         |

| С       |           | 1       | . –       | u       | ••-       |

| d       |           | m       |           | V       | • • • –   |

| e       |           | n       |           | W       | · – –     |

| f       | ··-·      | 0       |           | X       |           |

| g       |           | p       | . – – .   | у       | - ·       |

| h       |           | q       |           | Z       |           |

| I       |           | r       |           |         |           |

Для каждого применения имеется более или менее подходящий код. Так, для проведения операций над числами в компьютере рационально применять иной код, чем для передачи чисел по линии связи. В данной главе исследуются различия между отдельными кодами и даны указания по их специфическому применению.

Комбинацию нескольких символов кода называют словом (word). В последующем мы ограничимся технически важным случаем, в котором все слова одного кода имеют одинаковую длину n. В коде Морзе это не происходит. Если в код входит множество символов N, то  $N^n$  различных слов могут иметь длину n. Когда используются все  $N^n$  возможных слов одного кода, то в этом случае говорят о минимальном коде. При использовании менее чем  $N^n$  слов его называют избыточным кодом. Ниже можно найти описание наиболее употребительных кодов, их полное описание можно получить из [7-9].

#### 2.2. Двоичный код

Будучи универсальным, двоичный код является важнейшим в цифровых системах. В соответствии с определением, при котором применяются только символы 1 и 0, становится возможной обработка сигналов с помощью схемных элементов, работающих как переключатели. Также двоичный код позволяет использование арифметики, аналогичной арифметике десятичных систем. При этом двоичную систему счисления можно рассматривать как кодирование десятичной системы, где двоичное число состоит из слова, образованного символом  $c_i \in \{0,1\}$ . Символы сі одного слова называют в цифровой технике битами. Слово  $z_2$  в двоичном представлении формируется путем последовательного присоединения отдельных битов, как это показано ниже:

$$z_2 = c_{n-1}c_{n-2}\cdots c_1c_0\cdots c_{-m+1}c_{-m}. (2.1)$$

Двоичное число имеет п разрядов перед запятой и m разрядов после запятой. Отдельным битам присвоены, в соответствии с их позицией i в слове, весовые коэффициенты  $2^i$ . На основе этого можно рассчитать эквивалентное десятичное число  $z_{10}$ :

$$\begin{aligned} z_2 &= g(z_{10}) = \\ &= c_{n-1} \, 2^{n-1} + c_{n-2} \, 2^{n-2} + \dots + c_1 \, 2^1 + c_0 \, 2^0 + \\ &+ \dots + c_{-m+1} \, 2^{-m+1} + c_{-m} \, 2^{-m}. \end{aligned} \tag{2.2}$$

Рассмотрим в качестве примера двоичное число 10110,001<sub>2</sub>, которое в качестве такового отмечено символом 2. Оно интерпретируется как:

$$g(z_2) = 1 \cdot 2^4 + 0 \cdot 2^3 + 1 \cdot 2^2 + 1 \cdot 2^1 + 0 \cdot 2^0 + 0 \cdot 2^{-1} + 1 \cdot 2^{-2} + 1 \cdot 2^{-3} = z_{10} = 22,375_{10}$$

Двоичный (или дуальный) код обозначается как взвешенный, поскольку стоящие дальше влево биты обладают более высокими весовыми коэффициентами. Уравнение (2.2) можно рассматривать как правило, в соответствии с которым производится преобразование двоичных чисел в десятичные числа.

Преобразование же десятичных чисел в двоичные числа является более сложным. Его можно описать различными алгоритмами для целочисленной и дробной частей. В приведенном выше примере с числом 22,37510 алгоритм должен быть представлен следующим образом:

• Вначале формируется целочисленная часть двоичного числа. Для чего целочисленная часть десятичного числа последовательно делится на 2 и записывается остаток, пока не будет получен 0.

$$22:2=1$$

остаток 0 остаток 1 остаток 1

Соответствующее числу 22<sub>10</sub> двоичное число представляет собой 10110<sub>2</sub>.

• Второй шаг заключается в преобразовании дробной части десятичного числа в дробную часть двоичного числа. Вначале дробная часть десятичного числа умножается на 2. Целочисленная часть отделяется, она образует разряды двоичного числа с наименьшими значениями.

Процесс повторяется, как это показано ниже.

В данном примере мы видим, что остаток равен 0. Но не обязательно так всегда бывает. В нормальном случае дробная часть эквивалентного двоичного числа имеет бесконечно большое количество разрядов. В данном случае необходимо удовольствоваться определенным числом разрядов после запятой и этим ограничить точность.

В нашем случае  $0,375_{10}$  точно соответствует  $0,011_2$ . На основе целочисленной и дробной частей получаем искомое двоичное число  $10110,011_2$ .

## 2.3. Арифметические операции с фиксированной запятой в двоичной системе

В данной главе описываются арифметические операции с числами с фиксированной запятой. Арифметические операции с фиксированной запятой означают, что в них запятая всегда стоит на фиксированном месте. При этом место, на котором стоит запятая, ориентируется на позицию в запоминающем устройстве (ЗУ), на которой находится число. В этом случае нет необходимости реализовать запятую в аппаратуре компьютера. Она существует только в голове программиста. Мы ограничиваемся постоянной длиной слова *n*, как это имеет место в компьютерах. На основе этого можно обсудить проблему переполнения допустимой области.

#### 2.3.1. Целочисленное сложение в двоичной системе

Целочисленное сложение двух чисел A и B производится в двоичной системе точно так же, как и в десятичной системе — по разрядам. Как и там, в каждом разряде должны быть просуммированы обе двоичных цифры  $a_n$  и  $b_n$  и перенос из предыдущего разряда  $C_{n-1}$ .

При сложении возникают (табл. 2.2) новая сумма  $S_n$  и новый перенос  $C_n$ . В этой таблице дискретной линией разделены входные и выходные величины. Например:

$$+ \frac{011111110}{00110101}$$

перенос

$$11111100$$

$$= 10110011$$

В приведённом выше примере, чтобы не было переполнения, необходимо суммировать два числа длиной 8 бит, итог которых также должен иметь длину 8 бит.

**Таблица 2.2.** Сложение в двоичной системе со слагаемыми  $a_n$ ,  $b_n$  и переносом из предыдущего разряда  $C_{n-1}$ . Сумма равна  $S_n$ , новый перенос  $C_n$

| $a_n$ | $b_{n}$ | $c_{n-1}$ | $C_n$ | $S_n$ |

|-------|---------|-----------|-------|-------|

| 0     | 0       | 0         | 0     | 0     |

| 0     | 0       | 1         | 0     | 1     |

| 0     | 1       | 0         | 0     | 1     |

| 0     | 1       | 1         | 1     | 0     |

| 1     | 0       | 0         | 0     | 1     |

| 1     | 0       | 1         | 1     | 0     |

| 1     | 1       | 0         | 1     | 0     |

| 1     | 1       | 1         | 1     | 1     |

#### 2.3.2. Сложение чисел с фиксированной запятой

В случае когда суммируются два числа с фиксированной запятой, важно, как и в обычной процедуре, чтобы обе запятые стояли друг над другом. Так, при сложении двух чисел длиной в 8 бит запятая у обоих чисел должна стоять, например, на третьем месте.

Например:

$$\begin{array}{r}

+ 01100,010 \\

00110,111

\end{array}$$

$$\begin{array}{r}

\text{перенос } 1100110 \\

= 10011,001

\end{array}$$

#### 2.3.3. Представление с помощью обратного кода

Для того, чтобы иметь малые затраты на аппаратурную часть (hardware) компьютера, были предприняты усилия по сведению к одному

алгоритму вычитания и сложения. Этого можно добиться, если применять двоичные цифры в их дополняющей форме. Различают единичное дополнение (обратный код, поразрядное дополнение) и двойное дополнение (точное дополнение).

Поразрядное дополнение формируется путем замены всех нулей на единицы и обратно. Следовательно, поразрядным дополнением (one's complement) 0001 является 1110. Ниже поразрядное дополне ние двоичного числа A обозначено  $\neg A$ . Очевидно, что при представлении n-битового слова имеем:

$$\neg A + A = 2^n - 1. \tag{2.3}$$

Например, при представлении 8-битового слова имеем:

$$10110011 + 01001100 = 111111111 = 2^8 - 1.$$

Можно так преобразовать уравнение (2.3), чтобы получить формулу для расчета поразрядного дополнения:

$$\neg A = 2^n - 1 - A. \tag{2.4}$$

## 2.3.4. Представление с помощью двойного дополнения (точное дополнение, two's complement)

Точное дополнение  $A_{K2}$  образуется из поразрядного дополнения  $\neg A$  путем прибавления 1:

$$A_{K2} = -A + 1. (2.5)$$

Следовательно, с учетом (2.4) будет справедливо:

$$A_{K2} = 2^n - A. \tag{2.6}$$

Мы видим, что в данном представлении содержится «-A», благодаря чему оно удобно для проведения вычитания. Учтем также, что  $2^n$  в двоичном представлении имеет n+1 разрядов. Ниже пример точного дополнения для 10101100:

$$A_{K2} = \neg A + 1 = 01010011 + 1 = 01010100$$

Представление 4-битовых двоичных слов в круговой форме, приведенное на рис. 2.1, позволяет показать числовой диапазон. Соответствующее данным значениям наибольшее представляемое положительное число равно  $7_{10}$ , соответствующее данным значениям наибольшее отрицательное число равно  $-8_{10}$ . Следовательно, числовой диапазон построен несимметрично, поскольку отрицательное число занимает больше места, чем положительное. Наибольшее и наименьшее представляемые числа можно выразить как:

$$z_{max} = 2^{n-1} - 1, (2.7)$$

$$z_{min} = -2^{n-1}. (2.8)$$

На рис. 2.1 можно видеть, что малые числа, сформированные на основе точного дополнения, содержат много ведущих единиц, когда они отрицательны, и содержат много ведущих нулей, когда они положительны. В числах, представленных в формате дополнения до двух, на крайней позиции слева стоит нуль, когда они отрицательны, и единица, когда они положительны. Их собственным точным дополнением является число

$1000_2$  ( $-8_{10}$ ). Важно установить, что при представлении на основе точного дополнения имеем только один 0. Это облегчает запрос, равен ли результат 0. Напротив, при представлении на основе поразрядного дополнения имеют место двоичное число  $0000_2$ , соответствующее  $+0_{10}$ , и двоичное число  $1111_2$ , соответствующее  $-0_{10}$ .

Рис. 2.1. Представление 4-битовых слов с помощью 4-битового дополнения

## 2.3.5. Вычитание при представлении с помощью точного дополнения

Пусть будут вычтены одно из другого два положительных двоичных числа A и B. При условии применения точного дополнения в соответствии с уравнением (2.6) вычитание можно провести следующим образом:

$$A - B = A - B + B_{K2} - B_{K2} = A - B + B_{K2} - (2^{n} - B).$$

(2.9)

Раскрытие скобок в правой части уравнения дает:

$$A - B = A + B_{K2} - 2^{n}. (2.10)$$

Что означает вычитание  $2^n$ ? Поясним это на примере операции вычитания 7-3=4 в 4-битовой двоичной системе. Сумма двоичного эквивалента числа 7 и дополнение двоичного эквивалента числа 3 равняется:

$$\begin{array}{r}

+ 0111 & 7_{10} \\

1101 - 3_{10}

\end{array}$$

$$= 10100 \\

- 10000 \\

= 0100 & 4_{10}

\end{array}$$

Вычитание числа  $10000_2$ , проведенное в соответствии с уравнением (2.10), дает правильный результат  $0100_2$ . Это может произойти в 4-битовом компьютере просто потому, что высший результат игнорируется. Итак, при проведении вычитания с помощью точного дополнения нет необходимости учитывать высший перенос  $c_4$ . Но необходимо соблюдать осторожность в связи с переполнением числового диапазона. Исследуем это ниже.

#### 2.3.6. Переполнение числового диапазона

Исходя из вышесказанного, возникает необходимость рассмотрения проблемы переполнения числового диапазона (overflow) в связи с представлением на основе точного дополнения. Переполнение числового диапазона может происходить только в двух случаях. А именно, когда суммируются два положительных числа либо суммируются два отрицательных числа. В связи с этим рассмотрим несколько примеров, относящихся к 4-битовому представлению.

Пример переполнения числового диапазона при сложении двух положительных чисел:

$$\begin{array}{r} +0101 & 5_{10} \\ 0101 & 5_{10} \\ \hline = (0)1010 & -6_{10} \end{array}$$

Очевидно, что результат является неправильным. Ошибка возникает за счет переноса 3-го разряда на место 4-го разряда, что приводит к симуляции отрицательного числа. Этот перенос  $c_3$  в представлении, использующем п бит, обычно обозначается как  $c_{n-1}$ . Перенос  $c_4$  (в общем случае  $c_n$ ) из разряда 4 в разряд 5 называется Carry (Cy). В этом примере данный перенос не имеет места.

• Пример переполнения численного диапазона при сложении отрицательных чисел:

В этом примере также появляется неправильный результат. Имеет место не перенос  $c_{{}_{n-1}}$  из разряда 3 в разряд 4, а перенос  $c_{{}_{n}}$  из разряда 4 в разряд 5.

• Для сравнения проведем сложение двух отрицательных чисел без переполнения числового диапазона:

Имеются переносы  $c_n$  и  $c_{n-1}$ .

Сведем эти результаты вместе с другими, здесь не показанными случаями в таблицу. На основе результатов, представленных в табл. 2.3, для двух двоичных чисел A и B, которые лежат в числовом диапазоне, определяемом n-битовым представлением на базе точного дополнения, можно установить перенос переполнения при сложении.

**Таблица 2.3.** Перенос переполнения при сложении в случае *n*-битового представления на основе точного дополнения

| Правильный результат         |                        | Перенос переполнения   |  |

|------------------------------|------------------------|------------------------|--|

| A+B                          | $c_n = 0, c_{n-1} = 0$ | $c_n = 0, c_{n-1} = 1$ |  |

| $A - B \qquad c_n = c_{n-1}$ |                        | невозможен             |  |

| -A-B                         | $c_n = 1, c_{n-1} = 1$ | $c_n = 1, c_{n-1} = 0$ |  |

Следовательно, правильный результат имеет место тогда, когда  $c_n = c_{n-1}$ , неправильный результат — когда  $c_n \neq c_{n-1}$ .

#### 2.3.7. Умножение

Умножение выполняется так же, как и для десятичной системы. Рассмотрим пример умножения на основе двоичной системы для чисел  $10_{10} \times 11_{10} = 110_{10}$ :

$$\begin{array}{r}

& 1010 \\

& 1011

\end{array}$$

$$\begin{array}{r}

& 1010 \\

& 1010 \\

& 1010

\end{array}$$

$$\begin{array}{r}

& 1101110

\end{array}$$

Наибольший из ожидаемых результатов E умножения двух n-битовых слов представляет собой:

$$E = (2^{n} - 1) \cdot (2^{n} - 1) = 2^{2n} - 2^{n+1} + 1 \le 2^{2n} - 1$$

Следовательно, результат умножения двух n-битовых чисел имеет длину 2n бит. Но он меньше, чем максимальное представляемое с помощью 2n бит двоичное число  $2^{2n} - 1$ .

Сказанное выше справедливо для умножения положительных чисел. При вычислениях с использованием представления на основе точного дополнения могут быть применены специальные алгоритмы [41], или же числа на основе точного дополнения перед умножением следует преобразовать обратно в исходные значения, а результат перевести в соответствии со знаком в желаемое представление.

При умножении чисел с фиксированной запятой вначале числа умножаются без учета запятой. Затем запятая вводится в соответствии с правилом: умножение двух чисел с n и k разрядами после запятой даст произведение с n+k разрядами после запятой.

#### 2.3.8. Деление

Для деления можно использовать тот же самый алгоритм, что и в десятичной системе. Продемонстрируем это на примере уравнения  $10_{10}: 2_{10} = 5_{p}$ :

$$\begin{array}{c|c}

1010 & | & 0010 \\

-10 & & 101 \\

\hline

-010 & & \\

\hline

0 & & & \\

\end{array}$$

Соответственно, при делении числа с n разрядами после запятой на число с k разрядами после запятой частное имеет n-k разрядов после запятой. Так, в соответствии с верхним примером имеем  $(1,25_{10}:0,5_{10}=2,5_{10}):1,010:00,10=10,1$ . Деление чисел с точным дополнением также можно свести к умножению и сложению [41].

## 2.4. Представление вещественных чисел с плавающей запятой

## 2.4.1. Введение: представление с плавающей запятой в десятичной системе счисления

Большие числа обычно представляются в экспоненциальном виде с плавающей запятой. Примером может служить представление скорости света:  $2,99792458 \cdot 10^8$  м/с. В общем виде:

$$z = m \cdot b^e. \tag{2.11}$$

Число m называется мантиссой, а e — показателем степени. Здесь e — целое число, а m — число с фиксированной запятой со знаком. В этом примере мантисса равна 2,99792458, а показатель степени равен 8. Для представления чисел в формате с плавающей запятой характерно наличие основания b. В данном примере основание b = 10. И показатель степени, и мантисса имеют знак. В компьютерах используется представление в дво-ичной системе с основанием b = 2.

## 2.4.2. Представление с плавающей запятой в двоичной системе счисления

В этой главе описывается представление с плавающей запятой в двоичной системе счисления. В информатике эту форму представления числа называют «реальной», поскольку ее можно использовать для представления действительных чисел. Согласно стандарту IEEE-754 в общем случае представление чисел с плавающей запятой имеет следующий вид:

$$z = (-1)^s \cdot 1, m \cdot 2e = (-1)^s \cdot 1, m \cdot 2^{(c-q)}.$$

(2.12)

- s знак мантиссы, он представлен одним битом.

- 1, *m* абсолютное значение мантиссы. Оно хранится как двоичное число с фиксированной запятой и перед местом, обозначенным запятой. Оно всегда равно единице. Число *m* после запятой называется дробной частью. *m* выбирается согласно выбору показателя степени так, чтобы удовлетворять условию:

$$2 > |1, m| \ge 1. \tag{2.13}$$

Условие верно только для чисел  $z \neq 0$ . Следовательно, нельзя представить нуль. Форма записи с плавающей запятой, удовлетворяющая условию (2.13), называется нормализованной. Мантисса располагает в компьютере фиксированным количеством цифровых позиций  $n_{\rm m}$ .

• Вместо показателя степени е сохраняется характеристика c = e + q. Она имеет фиксированное количество цифр  $n_c$ . При добавлении остатка показатель степени е сдвигается так, чтобы сохранять только положительные числа. Остаток равен

$$q = 2^{nc-1} - 1. (2.14)$$

Таким образом, например, для 8 цифр ( $n_c = 8$ ) получим остаток 127. Это означает, что могут быть представлены показатели от -127 до 128. Наи-

меньшая характеристика 0 получается, когда наименьший показатель степени равен —127, и становится равной нулю при добавлении остатка 127. Наибольшая характеристика, а именно наибольшее число 255, которое может быть представлено 8 битами, получается из суммы наибольшего показателя 128 и остатка 127.