# **М**ектроники

А.И. Белоус, Г.Я. Красников, В.А. Солодуха

Основы проектирования субмикронных микросхем

ТЕХНОСФЕРА Москва 2020 УДК 621.3 ББК 32.844.1 Б43

Б43 Белоус А.И., Красников Г.Я., Солодуха В.А. Основы проектирования субмикронных микросхем Москва: ТЕХНОСФЕРА, 2020. – 782 с. ISBN 978-5-94836-603-6

В объеме 14 глав одной книги детально и последовательно рассмотрен весь комплекс взаимосвязанных теоретических и практических аспектов сквозного проектирования и организации производства кремниевых субмикронных микросхем: теоретические основы работы полевых и биполярных транзисторов, методы и особенности конструктивно-схематического проектирования, базовые схемотехнические и системотехнические решения биполярных, КМОП-, БиКМОП- и КНИ-микросхем, методы и средства повышения их радиационной стойкости, стандартные библиотеки проектирования и типовые маршруты проектирования.

Впервые в отечественной научно-технической литературе здесь детально рассмотрены методы логического проектирования КМОП-микросхем с пониженным энергопотреблением, а также основные принципы и методы проектирования кибербезопасных микросхем и систем-на-кристалле.

Детально рассмотрены современные методы и средства управления качеством изготовления субмикронных микросхем, современные технологии корпусирования микросхем, систем-на-кристалле и систем в корпусе.

Отдельная глава посвящена анализу состояния и тенденций развития современной микроэлектроники, включая методологический анализ существующих проблем и новых угроз.

Книга ориентирована на широкий круг читателей: студентов и преподавателей технических университетов, а также инженеров и менеджеров, специализирующихся в области разработки и организации производства субмикронных микросхем.

УДК 621.3 ББК 32.844.1

<sup>©</sup> Белоус А.И., Красников Г.Я., Солодуха В.А., 2020

<sup>©</sup> АО «РИЦ «ТЕХНОСФЕРА», оригинал-макет, оформление, 2020

### Содержание

| Вместо предисловия — дайджест                                        | . 5 |

|----------------------------------------------------------------------|-----|

| Введение                                                             | 25  |

| Глава 1. Физические основы работы полевых транзисторов               | 31  |

| 1.1. Физические основы работы субмикронных МОП-транзисторов 3        | 31  |

| 1.1.1. Типовая структура МОП-транзистора 3                           | 31  |

| 1.1.2. Глубина области обеднения                                     | 38  |

| 1.1.3. Определение величины заряда в слое инверсии                   | 39  |

| 1.1.4. Оценка толщины инверсионного слоя                             | 10  |

| 1.2. Анализ работы МОП-транзистора с длинным каналом                 | 11  |

| 1.2.1. Анализ влияния подложки на работу МОП-транзистора 4           | 11  |

| 1.2.2. Выражения для оценки значения допорогового тока               | 12  |

| 1.3. Анализ физических процессов, происходящих в субмикронном        |     |

| МОП-транзисторе                                                      | 15  |

| 1.3.1. Анализ физических эффектов, влияющих на пороговое             |     |

| напряжение МОП-транзистора4                                          | 15  |

| 1.3.2. Методы ограничения эффекта сквозного пробоя 5                 | 51  |

| 1.3.3. Эффект возникновения тока утечки стока МОП-транзистора,       |     |

| обусловленный влиянием его затвора5                                  |     |

| Литература к главе 1                                                 | 53  |

| Глава 2. Особенности конструктивно-схемотехнического проектирования  |     |

| субмикронных микросхем5                                              | 56  |

| 2.1. Основные проблемы проектирования микросхем с субмикронными      |     |

| проектными нормами5                                                  |     |

| 2.2. Основные тенденции развития кремниевых БИС 5                    | 59  |

| 2.3. Пути уменьшения величины потребления мощности                   |     |

| в субмикронных БИС                                                   | 53  |

| 2.4. Взаимосвязь утечки и статического потребления мощности          |     |

| в структуре субмикронного МОП-транзистора 7                          | 1   |

| 2.4.1. Пути уменьшения потребления мощности в субмикронных           |     |

| КМОП-БИС                                                             | 71  |

| 2.4.2. Анализ токов, протекающих в субмикронном                      |     |

| МОП-транзисторе                                                      | 4   |

| 2.4.3. Физические причины возникновения токов утечки                 |     |

| в субмикронных кремниевых транзисторах                               | !7  |

| 2.4.3.1. Подпороговый ток утечки $I_{SUB}$ субмикронного             | • • |

| МОП-транзистора                                                      |     |

| $2.4.3.2$ . Туннельный ток затвора $I_{\text{GATE}}$ МОП-транзистора |     |

| 2.4.3.3. Ток выключения $I_{off}$ МОП-транзистора                    | śÜ  |

| 2.4.3.4. Методы снижения величины статической мощности               | 1   |

| потребления МОП-транзистора 8                                        | śΙ  |

| 2.4.3.5. Особенности проектирования субмикронных                                |     |

|---------------------------------------------------------------------------------|-----|

| аналоговых и аналогово-цифровых БИС                                             |     |

| с учетом статического потребления мощности                                      | 83  |

| 2.5. Динамическое потребление мощности субмикронного                            |     |

| МОП-транзистора                                                                 | 87  |

| 2.5.1. Задержки распространения сигнала на внутренних                           |     |

| межсоединениях кристалла                                                        | 89  |

| 2.5.2. Методы снижения уровня динамической мощности                             |     |

| субмикронных БИС                                                                | 89  |

| 2.5.3. Анализ и расчет динамической мощности, обусловленной                     |     |

| токами утечки                                                                   |     |

| 2.6. Проблемы корпусирования субмикронных микросхем                             | 95  |

| 2.7. Методы обеспечения надежности передачи сигналов                            |     |

| в субмикронных микросхемах                                                      |     |

| 2.7.1. Использование стандартных библиотек проектирования                       | 98  |

| 2.7.2. Использование двух внутренних источников питающих                        |     |

| напряжений                                                                      | 98  |

| 2.8. Влияние температуры и разброса технологических параметров                  |     |

| на характеристики кремниевых субмикронных микросхем                             |     |

| 2.8.1. Учет зависимости токов утечки от температуры                             |     |

| 2.8.1.1. Температурная зависимость токов $I_{\mathit{on}}$ и $I_{\mathit{off}}$ |     |

| 2.8.1.2. Температурная зависимость подпорогового тока $I_{{\it SUB}}$           | 102 |

| 2.8.1.3. Температурная зависимость тока перехода $I_{\scriptscriptstyle JUNC}$  | 102 |

| 2.8.1.4. Температурная зависимость тока $I_{\it GIDL}$                          | 103 |

| 2.8.1.5. Температурная зависимость туннельного тока                             |     |

| затвора $I_{\it GATE}$                                                          | 104 |

| 2.9. Взаимосвязь разброса параметров технологического процесса                  |     |

| и численных значений токов утечки                                               | 105 |

| 2.9.1. Причины и виды отклонений технологических                                |     |

| и топологических параметров                                                     | 105 |

| 2.9.2. Оценка влияния разброса технологических параметров                       |     |

| на токи утечки                                                                  | 108 |

| 2.10. Особенности проектирования топологии аналоговых микросхем                 |     |

| с проектными нормами глубокого субмикрона                                       |     |

| 2.10.1. Учет влияния уменьшения напряжения питания                              | 112 |

| 2.10.2. Учет эффекта масштабирования и задержки                                 | 114 |

| распространения сигнала на межсоединениях кристалла                             | 114 |

| 2.11. Основные ограничения при проектировании КМОП-микросхем                    | 116 |

| с минимальным энергопотреблением                                                | 116 |

| 2.11.1. Физические ограничения при проектировании                               | 117 |

| маломощных КМОП-микросхем                                                       | 116 |

| 2.11.2. Конструктивно-технологические ограничения при                           | 110 |

| проектировании маломощных КМОП-микросхем                                        | 119 |

| 2.11.3. Схемотехнические ограничения при проектировании                         | 100 |

| маломошных КМОП-микросуем                                                       | 120 |

| 2.11.4. Системотехнические ограничения при проектировании    |     |

|--------------------------------------------------------------|-----|

| микромощных КМОП-микросхем                                   | 122 |

| 2.12. Основные рекомендации разработчикам конструкций        |     |

| кремниевых субмикронных микросхем                            | 125 |

| Литература к главе 2                                         | 129 |

| Глава 3. Основные характеристики цифровых микросхем          | 131 |

| 3.1. Структурная организация цифровых микросхем              |     |

| 3.1.1. Общая структура цифровых микросхем                    |     |

| 3.1.2. Структура внутренних элементов цифровых микросхем     |     |

| 3.1.3. Структура элементов согласования цифровых микросхем   |     |

| 3.2. Система основных параметров и характеристик цифровых    |     |

| микросхем                                                    | 149 |

| 3.2.1. Функциональные параметры цифровых микросхем           |     |

| 3.2.2. Электрические параметры цифровых микросхем            |     |

| 3.2.3. Динамические параметры цифровых микросхем             |     |

| 3.3. Схемотехническое исполнение цифровых микросхем          |     |

| 3.3.1. Энергетические характеристики базовых ЛЭ цифровых     |     |

| микросхем                                                    | 153 |

| 3.3.2. Схемотехническое исполнение базовых ЛЭ цифровых       |     |

| микросхем                                                    | 163 |

| 3.3.3. Методика выбора элементной базы цифровых микросхем    |     |

| 3.4. Влияние дестабилизирующих факторов на работоспособность |     |

| цифровых микросхем                                           | 168 |

| 3.4.1. Устойчивость цифровых микросхем к электростатическому |     |

| разряду                                                      | 169 |

| 3.4.2. Устойчивость цифровых микросхем к воздействию         |     |

| перегрузок                                                   | 175 |

| 3.4.3. Зависимость электрических характеристик цифровых      |     |

| микросхем от режимов эксплуатации                            | 176 |

| 3.4.4. Устойчивость цифровых микросхем к воздействию помех   | 178 |

| 3.5. Паразитные элементы и эффекты в цифровых микросхемах    | 191 |

| 3.5.1. Паразитные транзисторные элементы в кристаллах        |     |

| цифровых микросхем                                           | 191 |

| 3.5.2. Эффект Миллера                                        |     |

| 3.5.3. Эффект «защелкивания»                                 |     |

| Литература к главе 3                                         | 204 |

| Глава 4. Схемотехнические решения цифровых КМОП-микросхем    | 206 |

| 4.1. Базовые логические элементы цифровых КМОП-микросхем     |     |

| 4.1.1. Статические КМОП ЛЭ                                   |     |

| 4.1.2. Базовые ЛЭ динамической КМОП-логики                   |     |

| 4.2. Элементы памяти цифровых КМОП-микросхем                 |     |

| 4.2.1. Элементы памяти, тактируемые уровнем синхросигнала    |     |

| 4.2.2. Элементы памяти, тактируемые фронтом синхросигнала    |     |

| Литература к главе 4                                         | 250 |

| <b>Ілава 5.</b> Схемотехнические решения биполярных микросхем      | 252 |

|--------------------------------------------------------------------|-----|

| 5.1. Цифровые микросхемы на биполярных транзисторах                |     |

| с диодами Шоттки                                                   | 252 |

| 5.1.1. Базовые логические элементы ТТЛШ цифровых микросхем         | 253 |

| 5.1.2. Базовые ЛЭ Шоттки транзисторной логики                      | 260 |

| 5.1.3. Базовые ЛЭ Шоттки интегральной логики                       | 262 |

| 5.1.4. Базовые ЛЭ диодно-транзисторной логики с диодами            |     |

| Шоттки                                                             | 266 |

| 5.2. Элементы памяти ТТЛШ микросхем                                | 267 |

| 5.2.1. Элементы памяти, тактируемые фронтом синхросигнала          |     |

| 5.2.2. Элементы памяти, тактируемые уровнем синхросигнала          | 275 |

| 5.3. Схемотехника входных элементов согласования ТТЛШ              |     |

| микросхем                                                          | 277 |

| 5.3.1. Входные ЭС ТТЛШ микросхем со стандартными ТТЛ               |     |

| входными уровнями                                                  | 277 |

| 5.3.2. Входные ЭС ТТЛШ микросхем с повышенной                      |     |

| нагрузочной способностью                                           | 281 |

| 5.3.3. Входные ЭС ТТЛШ микросхем с парафазными выходами            | 283 |

| 5.3.4. Входные ЭС ТТЛШ микросхем с памятью                         | 285 |

| 5.3.5. Входные ЭС ТТЛШ микросхем с повышенной                      |     |

| помехоустойчивостью                                                | 288 |

| 5.3.6. Входные ЭС с преобразованием уровней сигналов               | 294 |

| 5.3.7. Схемы защиты цепей входных ЭС ТТЛШ микросхем                | 300 |

| 5.4. Схемотехника выходных элементов согласования ТТЛШ             |     |

| микросхем                                                          | 303 |

| 5.4.1. Выходные ЭС ТТЛШ микросхем со стандартными ТТЛ              |     |

| выходными уровнями                                                 | 303 |

| 5.4.2. Выходные ЭС ТТЛШ микросхем с памятью                        | 312 |

| 5.4.3. Выходные ЭС ТТЛШ микросхем с преобразованием уровней        |     |

| сигналов                                                           | 314 |

| 5.4.4. Схемотехника цепей защиты выходных ЭС ТТЛШ                  |     |

| микросхем                                                          | 317 |

| 5.5. Цифровые микросхемы на основе интегральной инжекционной       |     |

| логики                                                             | 330 |

| 5.5.1. Разновидности базовых элементов И <sup>2</sup> Л микросхем  | 334 |

| 5.5.2. Элементы памяти И <sup>2</sup> Л микросхем                  | 342 |

| 5.5.3. Схемотехника входных элементов согласования                 |     |

| И <sup>2</sup> Л микросхем                                         | 349 |

| 5.5.4. Защита выводов И <sup>2</sup> Л микросхем от перенапряжения |     |

| и статического электричества                                       | 364 |

| Литература к главе 5                                               | 364 |

| Глава 6. Схемотехнические решения БиКМОП-микросхем                 | 367 |

| 6.1. Базовые логические элементы БиКМОП-микросхемы                 |     |

| 6.2. Элементы памяти БиКМОП-микросхемы                             |     |

|                                                                    |     |

| 6.3. Схемотехника входных элементов согласования БиКМОП-         |     |

|------------------------------------------------------------------|-----|

| микросхемы                                                       | 381 |

| 6.3.1. Входные ЭС БиКМОП-микросхемы с преобразованием            |     |

| уровней сигналов                                                 | 381 |

| 6.3.2. Входные ЭС БиКМОП-микросхемы с повышенной                 |     |

| нагрузочной способностью                                         | 387 |

| 6.3.3. Входные ЭС БиКМОП-микросхемы с парафазными                |     |

| выходами                                                         | 387 |

| 6.3.3. Входные ЭС БиКМОП-микросхемы повышенной                   |     |

| помехозащищенности                                               | 388 |

| 6.3.4. Входные ЭС БиКМОП-микросхемы с памятью                    | 389 |

| 6.3.5. Схемотехника цепей защиты входных ЭС БиКМОП-              |     |

| микросхемы                                                       | 389 |

| 6.4. Схемотехника выходных элементов согласования БиКМОП-        |     |

| микросхемы                                                       | 390 |

| 6.4.1. Выходные ЭС БиКМОП-микросхемы с формированием             |     |

| КМОП выходных уровней                                            | 390 |

| 6.4.2. Выходные ЭС БиКМОП-микросхемы с формированием             |     |

| ТТЛ выходных уровней                                             | 391 |

| 6.4.3. Выходные ЭС БиКМОП-микросхемы с формированием             |     |

| ЭСЛ выходных уровней                                             | 395 |

| 6.4.4. Выходные ЭС БиКМОП-микросхемы с памятью                   |     |

| 6.4.5. Схемотехника цепей защиты выходных ЭС БиКМОП-             |     |

| микросхемы                                                       | 397 |

| Литература к главе 6                                             |     |

|                                                                  |     |

| Глава 7. Особенности проектирования радиационностойких микросхем |     |

| на основе КНС и КНИ-структур                                     |     |

| 7.1. Радиационно-стойкие КМОП БИС на основе КНИ-структур         | 400 |

| 7.2. Воздействие ионизирующего облучения на кремний и двуокись   |     |

| кремния                                                          |     |

| 7.2.1. Радиационные эффекты в кремнии при облучении              |     |

| 7.2.1.1. Радиационные дефекты, их комплексы и кластеры           | 410 |

| 7.2.1.2. Особенности дефектообразования в кремнии и              |     |

| поликремнии, облученном импульсами гамма-квантов                 |     |

| 7.2.2. Свойства границы раздела Si/SiO <sub>2</sub>              |     |

| 7.2.2.1. Общие сведения о строении SiO <sub>2</sub>              |     |

| 7.2.2.2. Электронная структура SiO <sub>2</sub>                  | 414 |

| 7.2.3. Воздействие ионизирующего облучения на диэлектрические    |     |

| слои                                                             | 417 |

| 7.3.3.1. Введение объемного заряда в диэлектрик                  | 417 |

| 7.2.3.2. Образование быстрых поверхностных состояний             | 418 |

| 7.2.3.3. Влияние радиации на проводимость диэлектрических        |     |

| слоев                                                            | 418 |

| 7.2.3.4. Отжиг облученных лиэлектрических слоев                  | 419 |

| 7.2.3.3. Исрархия времен радиационно-индуцированных               |     |

|-------------------------------------------------------------------|-----|

| процессов в структурах с диэлектриком                             | 419 |

| 7.2.3.6. Пути повышения стабильности структур                     |     |

| с диэлектрическими слоями                                         | 419 |

| 7.2.4. Радиационные процессы в скрытом диэлектрике структур       |     |

| кремний-на-изоляторе                                              | 420 |

| 7.2.5. Сравнение радиационных свойств КНИ-структур,               |     |

| полученных разными способами                                      | 422 |

| 7.3. Физические явления в МОП/КНИ-транзисторах в условиях         |     |

| воздействия ИИ                                                    | 424 |

| 7.3.1. Ионизирующее излучение                                     | 424 |

| 7.3.1.1. Единичные сбои                                           | 425 |

| 7.3.1.2. Единичная защелка                                        | 428 |

| 7.3.1.3. Единичное выгорание                                      | 428 |

| 7.3.1.4. Единичный пробой затвора                                 | 429 |

| 7.3.1.5. Единичное восстановление (однотранзисторная              |     |

| защелка)                                                          | 429 |

| 7.3.2. Эффекты полной дозы                                        | 429 |

| 7.3.3. Эффекты импульсного облучения                              | 433 |

| 7.4. Результаты экспериментальных исследований образцов           |     |

| элементной базы КМОП БИС на КНИ-структурах                        | 435 |

| 7.4.1. Состав тестовых элементов                                  | 435 |

| 7.4.2. Методика проведения эксперимента                           | 438 |

| 7.4.3. Экспериментальные результаты                               | 440 |

| 7.4.3.1. Резисторы                                                | 440 |

| 7.4.3.2. Диоды                                                    | 443 |

| 7.4.3.3. Конденсаторы                                             | 445 |

| 7.4.3.4. Транзисторы                                              | 448 |

| Литература к главе 7                                              | 458 |

| Глава 8. Библиотеки проектирования субмикронных микросхем —       |     |

| структура и особенности                                           | 459 |

| 8.1. Маршрут процесса разработки библиотеки проектирования,       |     |

| структура стандартного РДК                                        | 459 |

| 8.2. Термины и определения, используемые при описании             |     |

| компонентов РDК                                                   | 461 |

| 8.3. Стандартизация PDK                                           |     |

| 8.4. Маршрут проектирования смешанных аналогово-цифровых          |     |

| микросхем                                                         | 467 |

| 8.5. Обобщенная информационная модель проектирования              |     |

| смешанных аналогово-цифровых ИМС                                  | 469 |

| 8.6. Определение состава базовой библиотеки проектирования        |     |

| и перечня стандартных элементов                                   | 471 |

| 8.7. Особенности разработки цифровых библиотек для проектирования | 1/1 |

| заказных ИМС с субмикронными проектными нормами                   | 473 |

|                                                                   |     |

| 8.8. Конструктивно-схемотехнические особенности проектирования |     |

|----------------------------------------------------------------|-----|

| базовых элементов библиотеки субмикронных микросхем            | 482 |

| 8.8.1. Схемы сдвига уровня напряжений                          | 482 |

| 8.8.2. Схемы управления питанием                               | 484 |

| 8.8.3. Библиотечные элементы изоляции субмикронных             |     |

| микросхем                                                      | 485 |

| 8.8.4. Постоянно включенные буферы                             | 487 |

| 8.9. Типовые информационные файлы PDK библиотеки               |     |

| проектирования                                                 | 489 |

| 8.10. Стандартные модели источников тока (CCS) PDK             | 492 |

| 8.11. Способы и примеры адаптации стандартных инструментов     |     |

| проектирования ИМС к разработкам микросхем с проектными        |     |

| нормами 90, 65, 45 нм                                          | 494 |

| 8.11.1. Учебный (образовательный) дизайн-кит компании Synopsys | s:  |

| возможности, применение, перспективы                           | 494 |

| 8.11.2. Краткий обзор EDK компании Synopsys                    |     |

| 8.11.3. Стандартная библиотека цифровых компонентов            |     |

| фирмы Synopsys                                                 | 498 |

| 8.11.4. Стандартная библиотека элементов ввода-вывода          |     |

| 8.11.5. Стандартный набор модулей памяти РДК                   |     |

| 8.11.6. Цепь фазовой синхронизации PLL                         |     |

| 8.11.7. География применения и перспективы EDK                 | 502 |

| 8.12. Состав учебных дизайн-китов, предоставляемых Центром     |     |

| микроэлектроники ІМЕС                                          | 502 |

| Литература к главе 8                                           |     |

| Глава 9. Маршруты проектирования цифровых микросхем            |     |

| и систем-на-кристалле                                          |     |

| 9.1. Выбор маршрута проектирования микросхемы                  |     |

| 9.2. Этап системного проектирования                            |     |

| 9.3. Этап функционального проектирования                       |     |

| 9.4. Этап логического проектирования                           |     |

| 9.5. Этап физического (топологического) проектирования         |     |

| 9.6. Этап физической верификации и подготовки к производству   |     |

| 9.7. Аттестация проекта                                        |     |

| 9.8. Маршруты проектирования систем-на-кристалле               | 523 |

| 9.8.1. Тенденции развития средств проектирования               |     |

| 9.8.2. Методология проектирования SoC                          |     |

| 9.8.3. Маршрут проектирования SoC                              |     |

| 9.8.4. Системное проектирование SoC                            |     |

| 9.8.5. Программные средства САПР для системного уровня         | 532 |

| 9.9. Практический пример моделирования системы-на-кристалле    | 534 |

| 9.9.1. Стандартный маршрут проектирования «СнК»                |     |

| фирмы Cadence                                                  | 534 |

| 9.9.2. Описание среды моделирования и верификации                 |     |

|-------------------------------------------------------------------|-----|

| 9.9.3. Проект в среде Cadence Incivise                            |     |

| Литература к главе 9                                              | 542 |

| Глава 10. Основы логического проектирования КМОП-микросхем        |     |

| с пониженным энергопотреблением                                   | 543 |

| 10.1. Основы логического синтеза КМОП-микросхем с пониженным      |     |

| энергопотреблением                                                | 543 |

| 10.2. Определение источников рассеиваемой мощности                |     |

| в КМОП-микросхемах                                                | 545 |

| 10.3. Вероятностная оценка вариантов оптимизации                  |     |

| по прогнозируемой переключательной активности узлов               |     |

| микросхемы                                                        | 547 |

| 10.4. Выбор элементного базиса при проектировании                 |     |

| КМОП-микросхем с пониженным энергопотреблением                    | 549 |

| 10.5. Логический синтез КМОП-микросхем в базисе библиотечных      |     |

| элементов                                                         | 551 |

| 10.6. Оптимизация двухуровневых логических схем с учетом          |     |

| рассеивания мощности                                              | 553 |

| 10.7. Выбор базовых вентилей технологически независимой           |     |

| функциональной схемы                                              | 554 |

| 10.8. Оптимизация многоуровневых логических схем из многовходовых |     |

| вентилей                                                          | 556 |

| 10.9. Оптимизация многоуровневых логических схем из двухвходовых  |     |

| вентилей                                                          |     |

| 10.10. Технологическое отображение                                | 560 |

| 10.11. Оценка энергопотребления спроектированных КМОП-микросхем   |     |

| на логическом и схемотехническом уровнях                          | 562 |

| 10.12. Технология проектирования КМОП-микросхем с пониженным      |     |

| энергопотреблением с использованием комплекса ЭЛС                 |     |

| 10.13. Архитектура программного комплекса ЭЛС                     |     |

| 10.14. Функциональные возможности программного комплекса ЭЛС      |     |

| Литература к главе 10                                             | 571 |

| Глава 11. Основы проектирования кибербезопасных микросхем         |     |

| и систем-на-кристалле                                             | 573 |

| 11.1. Основы безопасности проектирования микросхем                |     |

| 11.1.1. Постановка задачи                                         |     |

| 11.1.2. Анализ типового маршрута проектирования микросхем         | 575 |

| 11.1.3. Возможные типы атак                                       |     |

| 11.1.4. Основные различия между разработкой безопасных            |     |

| микросхем и разработкой безопасных программ                       | 577 |

| 11.1.5. Жизненный цикл разработки безопасного программного        |     |

| обеспечения                                                       | 578 |

| 11.1.6. Методы безопасного пректирования микросхем                | 579 |

|                                                                   |     |

| 11.2. Программно-аппаратные методы противодействия              |     |

|-----------------------------------------------------------------|-----|

| аппаратным троянам в микросхемах                                | 584 |

| 11.2.1. Защита данных                                           | 584 |

| 11.2.2. Защищенные архитектуры на RTL-уровне                    | 588 |

| 11.2.3. Реконфигурируемые архитектуры                           | 590 |

| 11.2.4. Репликация и другие методы защиты                       | 592 |

| 11.3. Проектирование с целью обеспечения безопасности           |     |

| системы-на-кристалле                                            | 594 |

| 11.3.1. Введение в проблему                                     | 594 |

| 11.3.2. Описание структуры модуля безопасности                  | 597 |

| 11.3.2.1. Введение в ІР-инфраструктуры                          | 597 |

| 11.3.2.2. Стандарт IEEE 1500                                    |     |

| 11.3.3. Структура модуля IIPS                                   |     |

| 11.3.4. Проектирование функций безопасности IIPS                | 603 |

| 11.3.4.1. Модели атак и стратегии по устранению                 |     |

| их последствий                                                  | 603 |

| 11.3.4.2. Примеры реализации простейших безопасных              |     |

| структур SoC                                                    | 606 |

| 11.3.5. Протокол испытаний микросхемы согласно стандарту        |     |

| IEEE Std. 1500                                                  | 614 |

| 11.3.5.1. Режимы работы элементов обвязки микросхемы            | 614 |

| 11.3.5.2. Особенности протокола тестирования SoC                |     |

| уровня IIPS                                                     | 616 |

| 11.3.6. Результаты моделирования демонстрационной версии        |     |

| безопасной SoC                                                  |     |

| 11.3.6.1. Временная диаграмма работы системы                    | 619 |

| 11.3.6.2. Методики обнаружения аппаратных троянов в SoC         | 621 |

| 11.3.6.3. Оценка необходимых аппаратные затрат                  |     |

| для выявления трояна                                            |     |

| 11.3.7. Описание дополнительных возможностей блока IIPS         |     |

| 11.4. Безопасная архитектура SoC                                |     |

| 11.4.1. Введение в проблему                                     |     |

| 11.4.2. Структура и принцип работы стандартной шины SoC         |     |

| 11.4.3. Организация и принцип работы дешифратора адреса         |     |

| 11.4.4. Структура и принцип работы блока арбитра                |     |

| 11.4.5. Описание работы системы-на-кристалле непосредственно    |     |

| после обнаружения аппаратного трояна                            | 637 |

| 11.4.6. Оценка аппаратных затрат на реализацию метода           |     |

| обеспечения безопасности                                        | 639 |

| 11.5. Использование «песочницы» как метода защиты от аппаратных |     |

| троянов в SoC                                                   |     |

| 11.5.1. Введение в проблему                                     |     |

| 11.5.2. Песочница как инструмент обеспечения безопасности       | 645 |

| 11.5.3. Анализ сходных направлений решения проблемы             |     |

| безопасности проектирования SoC                                 | 646 |

| 11.5.4. Особенности организации процедур перемещения              |     |

|-------------------------------------------------------------------|-----|

| аппаратных троянов в песочницу при проектировании SoC             | 648 |

| 11.5.5. Основные программные методы помещения в песочницу         | 649 |

| 11.5.6. Типовая структура аппаратной песочницы                    | 650 |

| 11.5.7. Описание типового процесса проектирования                 |     |

| защищенной SoC                                                    | 652 |

| 11.5.8. Анализ практических примеров реализации песочницы в SoC.  | 655 |

| Литература к главе 11                                             |     |

| Глава 12. Основы построения системы управления качеством          |     |

| изготовления субмикронных интегральных микросхем на базе          |     |

| тестовых структур                                                 | 666 |

| 12.1. Методология организации технологического тестового контроля |     |

| в процессе проектирования и производства микроэлектронных         |     |

| изделий                                                           | 666 |

| 12.1.1. Место и роль полупроводниковых тестовых структур          |     |

| в процессе изготовления интегральных микросхем                    | 666 |

| 12.1.2. Классификация технологических тестовых структур           |     |

| 12.1.3. Способы размещения тестовых структур                      |     |

| на полупроводниковых пластинах                                    | 670 |

| 12.2. Принципы организации контроля процесса изготовления         |     |

| микросхем с использованием тестовых структур                      | 672 |

| 12.2.1. Оценка качества процесса на основе метода                 |     |

| межоперационного контроля пластин                                 | 672 |

| 12.2.2. Типовой состав тестового модуля контроля                  |     |

| производственных процессов                                        | 673 |

| 12.2.3. Типовой состав тестовых структур для контроля качества    |     |

| субмикронных микросхем                                            | 674 |

| 12.2.4. Статистическая обработка результатов измерений            |     |

| тестовых структур                                                 | 677 |

| 12.3. Прогнозирование процента выхода годных микросхем            |     |

| по результатам тестового контроля                                 | 678 |

| 12.3.1. Особенности моделирования процента выхода годных          |     |

| микросхем                                                         | 678 |

| 12.3.2. Модель пооперационного разделения дефектности             |     |

| технологического процесса изготовления микросхем                  | 682 |

| 12.4. Типовая структура системы тестового контроля качества       |     |

| технологических процессов                                         | 685 |

| 12.4.1. Особенности организации тестовых модулей                  |     |

| для биполярных и КМОП-микросхем                                   | 685 |

| 12.4.2. Типовой пример применения тестовых модулей                |     |

| для анализа технологического процесса изготовления                |     |

| в условиях серийного производства                                 | 689 |

| 12.5. Основные технологические факторы, влияющие на надежность    |     |

| микроэлектронных изделий                                          | 691 |

|                                                                   |     |

| 12.5.1. Основы теории надежности полупроводниковых приборов                                                              |     |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| и интегральных микросхем                                                                                                 | 691 |

| 12.5.2. Пути повышения надежности системы металлизации                                                                   |     |

| интегральных микросхем и полупроводниковых приборов                                                                      |     |

| Литература к главе 12                                                                                                    | 700 |

| Глава 13. Основные тенденции развития, проблемы и угрозы                                                                 |     |

| современной микроэлектроники                                                                                             | 703 |

| 13.1. Форсайт как инструмент долгосрочного прогнозирования                                                               |     |

| научно-технического развития                                                                                             | 703 |

| 13.2. Основные направления развития современной                                                                          | 705 |

| микроэлектроники                                                                                                         | 704 |

| 13.3. Использование новых материалов                                                                                     |     |

| 13.4. Смена драйверов развития                                                                                           |     |

| 13.5. Особенности экономики субмикронного производства                                                                   |     |

| 13.6. Усиление деструктивного действия эффекта Yield Killer                                                              |     |

| 13.7. Состояние и перспективы развития технологии FinFET в Китае                                                         |     |

| 13.8. Технологические проблемы современной микроэлектроники                                                              |     |

| 13.9. Тенденции развития космической микроэлектроники                                                                    |     |

| 13.10. Интегральная фотоника — новый этап в развитии                                                                     |     |

| микроэлектроники                                                                                                         | 718 |

| 13.11. Основы квантовой микроэлектроники                                                                                 |     |

| 13.12. Изменение парадигмы проектирования микросхем                                                                      |     |

| 13.13. Современная микроэлектроника и кибербезопасность                                                                  |     |

| 13.14. Принципиальные отличия «отечественных» и «зарубежных»                                                             |     |

| концепций разработки и использования ЭКБ                                                                                 |     |

| при проектировании РЭА                                                                                                   | 724 |

| 13.15. Микроэлектронная промышленность как основа суверенитета                                                           |     |

| России                                                                                                                   | 727 |

| Литература к главе 13                                                                                                    |     |

|                                                                                                                          |     |

| Глава 14. Технологии корпусирования микросхем                                                                            | /32 |

| 14.1. Основные тенденции развития технологий корпусирования                                                              | 722 |

| микросхем                                                                                                                |     |

| 14.2. ВGА-технология сборки кристаллов                                                                                   |     |

| 14.3. Технология монтажа кристаллов на плату                                                                             |     |

| 14.4. Многокристальные модули и печатные платы                                                                           | /40 |

| 14.5. Основные тенденции развития технологий корпусирования                                                              | 744 |

| высокоскоростных микроэлектронных устройств                                                                              |     |

| 14.5.1. Тенденция уменьшения шага выводов корпуса микросхем                                                              |     |

| 14.5.2. Технология сборки на пластине (WLP)                                                                              |     |

| 14.6. Технологии TSV сборки микросхем                                                                                    | /33 |

| 14.7. Особенности сборки 3D-изделий с использованием технологии                                                          | 760 |

| «flip-chip»                                                                                                              | /60 |

| 14.8. Основные тенденции развития технологии корпусирования микроэлектронных излелий космического и военного назначения. | 762 |

| микроэлектронных изделии космического и военного назначения.                                                             | /03 |

## [14] Содержание

| 14.9. Специализированные радиационно-защитные корпуса      |     |

|------------------------------------------------------------|-----|

| микросхем                                                  | 768 |

| 14.9.1. Современные материалы и конструкции корпусов       |     |

| с интегрированными элементами радиационной защиты          | 768 |

| 14.9.2. Экспериментальные исследования экранов             |     |

| радиационной защиты на основе различных материалов         | 773 |

| 14.9.3. Корпуса для микросхем с ЭРЗ на основе композитного |     |

| материала W-CU                                             | 777 |

| Литература к главе 14                                      | 778 |

#### Вместо предисловия – дайджест

Предлагаемая вниманию читателя книга ориентирована в первую очередь на студентов, преподавателей, магистрантов, инженерно-технических работников, специализирующихся в области микроэлектроники и ее многочисленных приложений. Кроме того, материалы книги могут быть полезны ученым, специалистам в области разработки, организации производства и эксплуатации радиоэлектронных устройств и систем бытового, промышленного и специального (космического и военного) назначения. Фактически материалы книги представляют собой практическое руководство (Handbook) по проектированию современных кремниевых субмикронных цифровых микросхем и систем на кристалле.

На момент выхода этой книги имеется достаточно много аналогичных книг (учебников и методических пособий), опубликованных в ведущих зарубежных издательствах. Так, например: «Handbook of Digital CMOS Technology, and System» Abbas Karim; « Handbook of Digital Technology for High Speed Design» автора Тома Гранберга; «Design Techniques for High-Frequency CMOS Integrated Circuits: From 10 GHz To 100 GHz» автора Zhiming Deng; « High-Speed Digital System Design. Art, Science and Experience» авторы А.И. Белоус, В.А. Солодуха; «Space Microelectronics Volume 2: Integrated Circuit Design for Space Applications» авторы А.И. Белоус, В.А. Солодуха, С.В. Шведов. По отдельным аспектам этого направления имеется достаточно много и отечественных изданий: «Электроника» авторов В.И. Лачин, Н.С. Савелов; «Конструктивно-технологические особенности субмикронных МОП-транзисторов» Г.Я. Красникова; «Основы силовой электроники» А.И. Белоус, В.А. Солодуха, С.А. Ефименко, В.А. Пилипенко; «Космическая электроника» А.И. Белоус, В.А. Солодуха, С.В. Шведов; «Основы схемотехники микроэлектронных устройств» А.И. Белоус, В.А. Емельянов, А.С. Турцевич; «Цифровая схемотехника» Е.П. Угрюмов и др.

В этих книгах на хорошем уровне детально рассматриваются различные частные аспекты комплексной проблемы проектирования и организации производства интегральных схем. Еще одним полезным источником информации являются статьи в наиболее популярных специализированных периодических научно-технических журналах — это достаточно общедоступный источник информации, но, как известно, журнальная статья также обычно посвящена только одной и достаточно узкой технической проблеме.

Авторы сами много лет читают лекции российским и белорусским студентам и хорошо понимают остроту этой проблемы как для студентов, так и для преподавателей.

Конечно, всегда «под рукой» есть интернет, где можно оперативно найти необходимую информацию, но здесь «беда» в том, что эта актуальная информация — как правило — на английском языке.

Образно говоря, отечественные студенты и инженеры, специализирующиеся в области микроэлектроники и ее приложений, могут получить из этих книг, статей и социальных сетей детальное и качественное описание отдельных «деревьев», но им приходится прилагать значительные усилия, чтобы увидеть общую картину «леса».

Поэтому авторы поставили перед собой достаточно амбициозную задачу — создать целостную картину такого «микроэлектронного леса», состоящего из отдельных «деревьев» (глав). В каждой из вошедших в книгу  $14\,$ глав детально и последовательно

рассмотрены основные этапы (направления) создания современной микросхемы — от детального описания физических механизмов работы базового транзистора, описания конструктивно-технологических и схемотехнических особенностей до базовых библиотек, маршрутов проектирования, инновационных технологий микромонтажа микросхем и систем на кристалле, методов проектирования кибербезопасных микросхем, систем на кристалле и заканчивая «деревом» — главой, посвященной анализу состояния, проблемам и перспективам развития современной микроэлектроники.

При этом авторы руководствовались следующими *принципами* построения материалов глав, которые было достаточно просто сформулировать, но оказалось достаточно тяжело выполнить в процессе написания книги:

- 1. Чтобы стать достаточно популярным изданием среди широкого круга читателей (инженеров и студентов), книга должна выполнять одновременно интегральные функции и классического учебника, и краткого справочника, да и просто увлекательной книги.

- 2. В книге должен быть представлен достаточно объемный справочный материал, но в отличие от классических учебников с изобилием формул, математических выражений, попытаться максимально простым языком изложить как основные теоретические аспекты исследуемой проблемы, так и основные методы и средства ее решения. В частности, привести конкретные практические примеры проектирования современных микросхем.

- 3. В книгу должны включаться только те методы, схемотехнические и технологические решения, эффективность которых ранее была подтверждена практикой их применения.

- 4. В тексте книги необходимо использовать максимально возможное количество графического материала, отражающего эффективность различных рабочих сценариев.

#### Теоретические основы работы полевых транзисторов

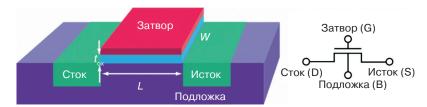

Прежде всего следует подчеркнуть, что каждый разработчик должен хорошо понимать физику работы базового элемента микросхемы — транзистора. Поэтому в первой вводной главе этой книги изложены теоретические основы работы классических полевых транзисторов, подробно рассмотрены физические основы работы современных субмикронных транзисторов, особенности работы классического полевого транзистора с длинным каналом (механизмы влияния подложки, математические выражения для оценки величины допорогового тока и др.), подробно описаны механизмы основных физических процессов, происходящих в субмикронном транзисторе, в том числе физические эффекты, влияющие на величину порогового напряжения транзистора и методы ограничения эффекта сквозного пробоя, а также эффекты возникновения токов утечки стока МОП-транзистора, обусловленные влиянием его затвора.

#### Особенности конструктивно-схемотехнического проектирования

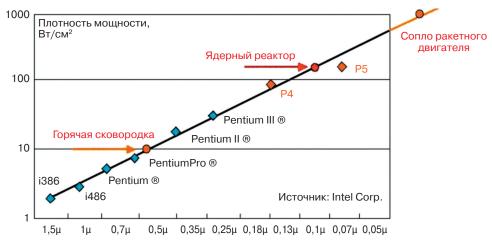

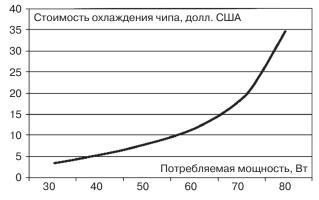

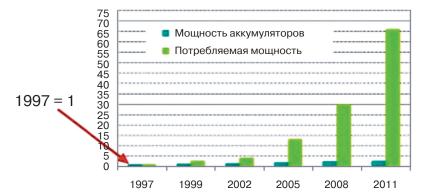

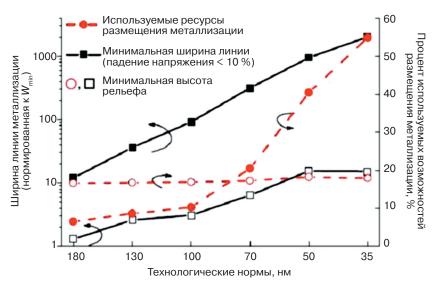

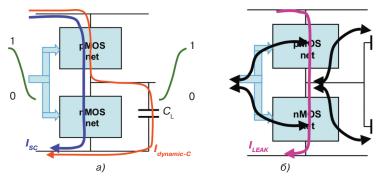

В объеме отдельной главы представлены результаты детального анализа особенностей конструктивно-схемотехнического проектирования современных субмикронных КМОП-микросхем, основные проблемы и тенденции развития кремниевых микросхем, пути уменьшения потребляемой мощности, анализируются физические

взаимосвязи между токами утечки и величиной статической мощности, между токами утечки и величиной динамической мощности, а также пути и методы уменьшения суммарной величины потребляемой микросхемой мощности.

Здесь же рассмотрены не менее важные вопросы обеспечения надежности (помехоустойчивости) передачи сигналов в субмикронных КМОП-микросхемах, а также физические эффекты влияния температуры и технологических разбросов параметров на технические характеристики кремниевых микросхем. Впервые в отечественной литературе детально проанализирована очень важная для практического использования взаимосвязь величин разброса параметров технологического процесса изготовления и токов утечки.

#### Основы схемотехники микроэлектронных устройств

Следует обратить внимание читателей на тот факт, что большой объем материала (четыре главы) авторами посвящен изложению основ схемотехники современных микроэлектронных устройств (микросхем и систем на кристалле). Этот факт обусловлен тем, что наша книга устраняет ряд очевидных для специалистов в этой сфере «пробелов» в большом объеме существующей научной и научно-технической литературы по вопросам анализа особенностей работы, методам проектирования и основам практического применения цифровых микросхем в составе современных микроэлектронных устройств. Здесь представлен большой набор эффективных схемотехнических решений базовых элементов для реализации требований, предъявляемых к современным сложнофункциональным, высокопроизводительным и надежным микроэлектронным устройствам.

Эта тема заслуживает более подробного пояснения.

Как известно, процесс создания любой цифровой микросхемы состоит из двух основных взаимосвязанных этапов: *погического проектирования*, в ходе которого определяется логическая организация (архитектура), система команд, интерфейс, структура устройств управления и обработки данных, включая временную диаграмму работы, и *схемотехнического проектирования*, включающего в себя совокупность задач выбора технологического базиса, преобразования логических схем в электрические схемы на транзисторном уровне, выбора схемотехнических решений базовых элементов, способов синхронизации, проектирования цепей питания, устройств защиты от внешних и внутренних помех, зарядов статического электричества и т.д.

Если методология и пути решения задач этапа *погического* проектирования достаточно широко рассмотрены в многочисленных зарубежных и отечественных изданиях, то с этапом *схемотехнического* проектирования, к сожалению, дело обстоит иначе.

Так, в современной многочисленной учебной и научно-технической литературе детально рассмотрены методы построения различных функциональных узлов комбинационного (дешифраторы, мультиплексоры, демультиплексоры, сумматоры, умножители и др.) и последовательного типа — автоматы с памятью (триггерные устройства, регистры, счетчики и др.), рассмотрены различные методики и средства их автоматизированного проектирования.

При этом эти узлы и блоки представляются на уровне «квадратиков», описываемых на языке булевой алгебры («И», «НЕ», «И-НЕ», «ИЛИ-НЕ» и т.п.) или в виде условно-графических обозначений (D-триггер, R-S-триггер, DV-триггер и т.п.).

Конечно, эта процедура является обязательным и неотъемлемым начальным этапом сквозного процесса проектирования любого микроэлектронного устройства. Однако как разработчик, так и конечный пользователь микроэлектронного устройства должны понимать, что находится «внутри» этих блоков и узлов. Разработчику это необходимо, чтобы путем выбора соответствующих элементов (транзисторов) и их связей обеспечить требуемые значения электрических и динамических параметров проектируемого устройства. Пользователю или специалисту по эксплуатации этого микроэлектронного устройства необходимо знать «начинку» этих блоков, чтобы понимать особенности функционирования конкретного микроэлектронного устройства в различных режимах его эксплуатации.

Ведь даже структура такого простейшего «кирпичика» — устройства внутренней памяти микросхемы — D-триггера, может быть реализована десятками различных схемотехнических вариантов соединений между собой составляющих его транзисторов. А современный студент должен ясно понимать, как из этого синтезированного блока (набора «квадратиков») «получается» топология соответствующего участка полупроводникового кристалла микросхемы, где размещение транзисторов на поверхности кристалла за счет организации соответствующих связей и межсоединений этих транзисторов между собой и с другими блоками позволяет реализовать заданный алгоритм функционирования блока (узла).

Но ведь этот D-триггер может быть реализован по различным технологиям —  $KMO\Pi$ , Би $KMO\Pi$ , биполярный (TTЛШ, ЭЛС,  $И^2Л$ ), каждая из которых имеет свои «нюансы» — так появились эти четыре «схемотехнические» главы.

В этих «схемотехнических» четырех главах предлагаемой книги и решается такая комплексная задача — для основных базовых блоков современных микроэлектронных устройств приводятся многочисленные примеры их схемотехнической реализации на уровне транзисторов и их взаимосвязей. Показано, например, что тот же простейший D-триггер в зависимости от его схемотехнической реализации будет обеспечивать различные, нужные разработчику численные значения быстродействия, нагрузочной способности, помехоустойчивости, мощности потребления и т.д.

Дополнительной особенностью этих четырех «схемотехнических» глав книги является детальное описание различного рода устройств (элементов) согласования — входных и выходных, которые обеспечивают электрическое и временное согласование при работе микросхемы в конечном радиоэлектронном устройстве, а также приведенные здесь методы и схемотехнические решения всегда актуальной проблемы снижения энергопотребления современных микросхем.

Побудительным мотивом авторов к написанию этих «схемотехнических» глав явилось желание помочь широкому кругу студентов, преподавателей, инженеров, специализирующихся в области проектирования и эксплуатации различных микро-электронных устройств, понять физические механизмы протекания процессов, происходящих внутри этих «кирпичиков», из которых строятся современные микросхемы и системы на кристалле. Ведь именно схемотехнические решения базовых элементов микросхем определяют в конечном итоге численные значения электрических, статических и динамических характеристик, потребляемой мощности, быстродействия, помехоустойчивости и даже площади кристалла микросхемы.

В этой связи полезно будет вспомнить ряд основных «классических» изданий по данной тематике, написанных много лет назад, но которые до сих пор можно увидеть на рабочих местах современных инженеров «по электронике» и в книжных магазинах.

Наиболее близкое к обсуждаемой здесь теме и широко известное студентам издание, монография «Искусство схемотехники» — классический учебник по цифровой и аналоговой схемотехнике, была написана американскими ученымипрактиками Paul Harowitz из Harvard University и Winfield Hill из Rowland Institute for Science, Cambridge, Massachusetts, первое английское издание (Cambridge University Press) вышло в 1980 г. и впоследствии выдержало десятки изданий, и даже сегодня пользуется спросом у студентов.

Этот ажиотаж вокруг книги американских специалистов и ее популярность до сих пор среди широкого круга читателей объясняется, с одной стороны, широтой охвата предметной области — основ конструирования радиоэлектронных схем, обширной справочной информацией по элементной базе («кирпичикам», из которых состояли радиоэлектронные устройства на момент написания книги), а во-вторых, в отличие от классических учебников с изобилием математических выкладок и физических формул, авторы простым языком, на большом количестве понятных практических примеров изложили все основные (на то время) аспекты конструирования радиоэлектронных устройств, на уровне, доступном для понимания даже «слабо подготовленными» читателями.

За свою необычайную для такого ряда изданий популярность среди студентов и инженеров по электронике книга получила в 90-х годах прошлого века вполне заслуженное неофициальное звание — *«библия электроники»*.

Очевидно, что за прошедшие с момента написания этой книги более 40 (!) лет элементная база микросхем, радиоэлектронных устройств и систем, подчиняясь известному закону Мура, изменилась принципиально. Те самые «кирпичики», блестяще описанные в этой «библии электроники», давно уже вошли в состав более крупных «строительных блоков» (IP-блоки или «Intellectual properties»), из которых «собираются» современные микросхемы и системы на кристалле, появились и новые элементы, которые раньше просто нельзя было реализовать технологически, появились базовые элементы, работающие на совершенно новых физических принципах и механизмах.

Основное достоинство предлагаемой авторами книги и заключается в детальном описании принципов работы и правил применения этих современных базовых элементов в составе микроэлектронных устройств. Например, элементов, реализованных по современной биполярно-полевой технологии (БиКМОП или BiCMOS), на момент выхода последнего англоязычного издания «библии» просто не было, то же самое можно сказать и о микромощной КМОП-элементной базе.

До сих пор в учебных курсах многих вузов также используется книга авторов Титце У., Шенк К. «Полупроводниковая схемотехника: справочное руководство». Пер. с нем. Halbleiter — Schaltungstechnik/ под ред. А.Г. Алексенко. — М.: Мир, 1982. В Германии и в России эта книга выдержала более двадцати изданий. Хотя в этой книге рассматриваются всего лишь структуры простейших полупроводниковых элементов, которые сегодня практически не используются в микроэлектронных устройствах (за исключением элементов силовой электроники, детально исследованных в той книге). Тем не менее очередные русскоязычные версии этого спра-

вочного руководства до сих пор периодически выпускаются издательствами, в том числе российскими, и пользуются спросом у специалистов и студентов, поскольку в продаже до сих пор отсутствовали более «современные» издания.

Сегодня на книжных рынках США, Англии и Европы присутствует и ряд других книг, посвященных схемотехнике современных микроэлектронных устройств, однако большинство из них рассматривают только отдельные составные части комплексной проблемы проектирования и содержат описания частных технологий (методы снижения рассматриваемой мощности, повышения производительности, способы моделирования, защиты от паразитных эффектов и т.д.) применительно к конкретным технологическим базисам — КМОП, биполярным, БИКМОП, КНИ (SOI) и др.

#### Радиационная стойкость микроэлектронных устройств.

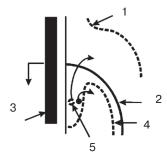

В последнее время существенно усилились требования к радиационной стойкости микросхем, предназначенных для использования в военной и космической технике. Поэтому авторы включили в книгу специальную главу, посвященную особенностям проектирования радиационно-стойких микросхем на основе КНС и КНИ-структур, в которой детально рассмотрены физические явления, происходящие в процессе воздействия ионизирующего излучения на кремний и двуокись кремния: механизмы образования радиационных дефектов и их кластеров, воздействие излучений на свойства границы раздела Si/SiO,, физические механизмы воздействия ионизирующих излучений на диэлектрические слои, особенности дефектообразования в кремнии (и поликремнии) при облучении гамма-квантами, радиационные изменения в «скрытом» диэлектрике КНИ-структур. Нами здесь детально рассмотрены и физические явления в МОП-транзисторах на КНИ-подложке в условиях воздействия ионизирующих излучений: единичные «сбои», единичные «защелкивания» (тиристорные эффекты), единичное «выгорание», пробой затвора, а также так называемые эффекты полной дозы. Достоинством этой главы является тот факт, что здесь мы дополнительно представили описание конкретных топологических решений и результаты статистического анализа наших конкретных экспериментальных исследований библиотечных элементов КНИ-микросхем (резисторы, диоды, конденсаторы и транзисторы).

#### Библиотеки проектирования субмикронных микросхем

В рамках еще одной отдельной «учебной» главы представлен состав, основные правила разработки и особенности применения библиотек проектирования субмикронных микросхем, которые в среде разработчиков называют «дизайн-китами» или PDK (от англ. Process Design Kits).

В последнее время в связи с возникновением самостоятельных (независимых от разработчиков микросхем) полупроводниковых фабрик, занимающихся заказным серийным производством микросхем (Integrated Ciruits Foundry — ICF), а также в связи с объективной необходимостью совместного использования стандартных средств проектирования и «покупных» IP-блоков (Intedectual Properties) от других компаний, именно библиотеки проектирования (PDK) стали основным связующим звеном между разработчиками микросхем и их изготовителями. В этой главе подробно рассматривается типовой маршрут процесса разработки и типовая структура PDK, минимальный состав базовой библиотеки и минимальный перечень стандартных

элементов, трансляторов уровней, модели источников тока, входные и выходные буферы, типовые информационные файлы библиотеки проектирования, а также приводится описание конкретного учебного (образовательного) PDK компании Synopsys.

#### Маршруты проектирования субмикронных микросхем

Эта глава посвящена изучению маршрутов проектирования современных субмикронных микросхем. Здесь рассмотрены особенности выбора конкретного маршрута проектирования в зависимости от исходных требований заказчика микросхемы, содержание основных этапов маршрута — системного, функционального и физического проектирования, финишной аттестации проекта. Подробно рассматриваются особенности проектирования микроэлектронных изделий более высокого уровня сложности — систем на кристалле: тенденции развития, детализированные маршруты проектирования, методологии проектирования, специфические особенности этапа системного проектирования систем на кристалле, базовый состав средств САПР для системного уровня. Для «закрепления» изученного материала будут приведены с авторскими комментариями понятные практические примеры выполнения процесса моделирования системы на кристалле, описанные в среде моделирования Саdance Incivise.

## Основы логического проектирования *КМОП*-микросхем с пониженным энергопотреблением

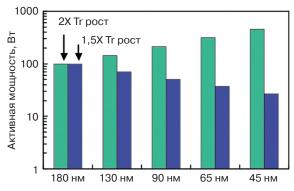

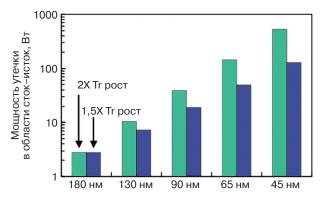

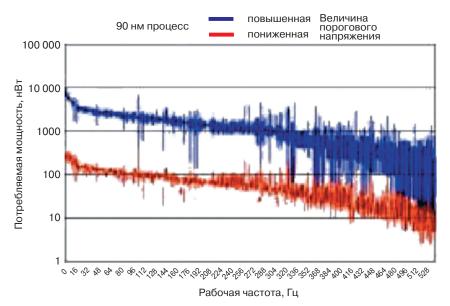

Глава посвящена рассмотрению особенностей логического проектирования КМОПмикросхем с пониженным энергопотреблением. Особенности развития современных субмикронных технологий заставляют разработчиков микросхем искать все новые методы и способы проектирования, направленные на снижение величины потребляемой мощности, обусловленной токами утечки, значение и вклад которых существенно возрастает с уменьшением проектных норм. В этой главе рассматриваются новые методы логического проектирования КМОП-микросхем с пониженным потреблением, основанные на использовании математического аппарата вероятностной оценки различных вариантов оптимизации по прогнозируемой так называемой переключательной активности основных блоков (узлов) проектируемой микросхемы. Представлены основные этапы такого логического проектирования от выбора требуемого элементного логического базиса, логического синтеза в этом выбранном базисе, процедуры оптимизации двухуровневых логических схем, оптимизации многоуровневых логических схем, построенных как на двухвходовых, так и на многовходовых логических вентилях, и завершая процедурами «технологического отражения» и оценки энергопотребления спроектированной (синтезированной) микросхемы как на логическом, так и схемотехническом уровнях.

В конце главы подробно описан соответствующий программно-аппаратный комплекс логического проектирования микромощных КМОП-микросхем.

#### Основы проектирования кибербезопасных микроэлектронных устройств

Как известно, в течение последнего десятилетия в мире произошла эволюция (изменение) традиционной парадигмы проектирования микросхем, обусловленная техническим феноменом возможности появления в микросхемах встроенных «кем-то» разнообразных *аппаратных троянов*.

Эти трояны могут выполнять по команде своего «хозяина» самые разные несанкционированные и скрытые от разработчика аппаратуры функции: передавать «хозяину» любую секретную информацию, изменять режимы функционирования, электрические режимы работы микросхемы — вплоть до ее отказа. Попадая на платы электронных блоков электронной аппаратуры, компьютеров, систем управления высокоточным оружием, систем энергообеспечения мегаполисов, систем управления магистральными газопроводами и т.п., эти «заряженные» микросхемы способны не только организовывать передачу «хозяину» информации, но и полностью «перехватывать» управление этими объектами — вплоть до приведения их в неработоспособное состояние. В книге «Кибербезопасность объектов топливно-энергетического комплекса — концепции, методы и средства обеспечения» (издательство «Инфра-Инженерия», 2020 г.) приведены многочисленные факты таких «инцидентов» на предприятиях нефтегазовой, энергетической отраслей и даже на атомных станциях.

В двухтомной технической энциклопедии А.И. Белоус, В.А. Солодуха, С.В. Шведов «Программные и аппаратные трояны — способы внедрения и методы противодействия», Техносфера, 2018, рассмотрены типы таких троянов, принципы их проектирования и функционирования, способы внедрения, методы маскировки, методы выявления, защиты и противодействия им. В фундаментальной работе А. Belous, V. Saladukha «Viruses, Hardware and Software Trojans» Springer Nature, 2020, авторами были описаны эффективные методы проектирования «кибербезопасных» систем на кристалле.

Проблема заключается в том, что если в современной сложнофункциональной *микросхеме* внедренный троян хотя и очень сложно (и очень дорого!), но можно обнаружить, то в современных *системах на кристалле* найти его среди миллионов похожих элементов практически невозможно.

В вышедшей в издательстве *Springer* вышеупомянутой книге мы рассмотрели ряд концепций и методов проектирования «кибербезопасных» микросхем и систем на кристалле — когда даже внедренный троян «изолируется», не влияет на работу микроэлектронного устройства и не может передавать «хозяину» информацию. Таким образом, авторы надеются изменить сложившуюся практику, когда актуальная зарубежная техническая литература издается в России в переводе с английского языка только через несколько лет после появления на мировом книжном рынке.

Здесь, в этой главе, фактически впервые в отечественной научно-технической литературе нами детально в доступной студенту форме изложены теоретические основы проектирования кибербезопасных (в отечественной терминологии — доверенных) микросхем и систем на кристалле, приведены результаты критического анализа стандартных типовых маршрутов проектирования микросхем на предмет возможных атак злоумышленников на каждом этапе (шаге) процесса такого «стандартного» проектирования.

В отдельном разделе этой главы детально рассмотрены также достаточно эффективные программно-аппаратные методы противодействия аппаратным троянам в микросхемах (способы защиты данных от несанкционированного считывания, защищенные архитектуры на RTL-уровнях, реконфигурируемые архитектуры микросхем и систем на кристалле, а также «репликация» и другие методы защиты.

#### Системы управления качеством изготовления микросхем

Как известно, спроектированная разработчиком микросхема затем обычно передается на полупроводниковую фабрику, для изготовления опытных (экспериментальных) образцов. Мировая практика за последнее десятилетие показывает, что только примерно 40% спроектированных микросхем после изготовления соответствуют исходной спецификации (техническому заданию), поэтому получить полностью соответствующие заданию изделия, да еще с «плановым» процентом выхода годных, иногда удается только после выполнения целого ряда последовательных итераций (корректировок). Для того чтобы повысить эффективность и сократить сроки анализа и выявления причин недостижения заданных характеристик или процента выхода годных спроектированной микросхемы, в технологическом маршруте часто используются специальные тестовые структуры, размещаемые на кристалле (пластине) спроектированной микросхемы. Понимание физических механизмов отказов микросхем необходимо не только для правильного выбора конструктивных решений микросхемы с учетом допустимых и критичных уровней плотности тока в активных полупроводниковых структурах и межсоединениях, напряженности электрического поля в диэлектрических слоях, но это необходимо и для разработки соответствующих мероприятий по выявлению и отбраковке потенциально ненадежных микросхем на различных стадиях серийного производства.

В этой главе будут рассмотрены основные принципы формирования таких «встраиваемых» в кристалл (или пластину) полупроводниковых тестовых структур, определение их перечня и функций, основы пооперационного прогнозирования надежности спроектированной микросхемы по результатам статистической обработки численных значений измеренных параметров таких тестовых структур. Здесь представлены и пояснены также математические модели, связывающие полученное статистическое распределение значений технических параметров микросхем с конкретными показателями надежности, приведены конкретные практические примеры оптимизации технологических процессов с помощью специальных тестовых пластин.

#### Современное состояние и перспективы развития микроэлектроники

Эта глава будет посвящена анализу основных тенденций развития, проблемам и угрозам современной микроэлектроники. Здесь на основе использования методов форсайта, как инструмента долгосрочного прогнозирования научно-технического развития, определены тенденции и основные тематические направления развития современной микроэлектроники, рассмотрена динамика изменения состава используемых в субмикронных технологиях новых веществ, компонентов и материалов, обосновано появление новых «движущих сил» развития микроэлектроники (драйверы развития), проанализированы некоторые важные, ранее не исследованные в отечественной научно-технической печати особенности экономики субмикронного производства. Среди проявляющихся технологических угроз особое внимание уделено усилению деструктивного действия известного эффекта «убийцы процента выхода годных» (Yield Killer).

Рассмотрено состояние и основные направления развития космической микроэлектроники, радиофотоники, квантовой микроэлектроники, состояние дел и перспективы развития инновационной технологии FinFET показано на конкретных примерах из опыта китайской полупроводниковой индустрии.

#### Корпусирование микроэлектронных устройств

В заключительной главе представлен анализ основных тенденций, перспектив и конкретных конструктивно-технологических решений, используемых в процессе корпусирования (микромонтажа) микроэлектронных устройств (микросхем, систем на кристалле, систем на пластине) различного назначения: это технологии BGA сборки кристаллов, WLP-сборки на пластине, TSV — трехмерной (3D) сборки, особенности сборки 3D-изделий на основе технологии «flip-chip», маршруты и технологии изготовления интерпоузеров.

В рамках отдельных параграфов здесь также будут рассмотрены конструкции и технологии изготовления специализированных радиационно-защитных конструкций корпусов для микросхем космического и военного назначения.

Далее во Введении представлена краткая аннотация каждой из вышеперечисленных глав этой книги.

В основу книги положены материалы семинаров лекционных курсов, много лет читаемых авторами в российских и белорусских вузах и академических институтах для студентов, аспирантов, магистрантов и преподавателей следующих специальностей: 5507002 «Электроника и микроэлектроника»; 551102 «Проектирование и технология электронных средств»; 5515002 «Приборостроение»; 5528002 «Информатика и вычислительная техника»; 2000003 «Электронная техника, радиотехника и связь»; 2100003 «Автоматика и управление» и др.

Кроме того, использованы результаты наших собственных исследований, опубликованных ранее в монографиях (в том числе за рубежом), патентах и статьях, а также результаты своей практической деятельности в области проектирования и применения микроэлектронных устройств.

#### Благодарности

Авторы выражают благодарность коллегам, активно участвовавшим в подготовке и обсуждении материалов книги, критические замечания, советы и дополнения которых способствовали улучшению как структуры книги, так и излагаемого в ней материала, — Борисенко В.Е., Бондаренко В.П., Стемпицкому В.Р., Силину А.В., Лынькову Л.М.

Особую благодарность авторы выражают коллегам, предоставившим нам оригинальные материалы собственных теоретических и практических исследований по тематике этой книги, включение которых в состав книги в значительной степени усилило практическую направленность работы: Бибило П.Н., Черемисинову Л.Д., Петлицкому А.Н., Петлицкой Т.В. и др.

Авторы выражают благодарность рецензенту — академику НАН Беларуси, иностранному избранному академику АН Российской Федерации Лабунову В.А., конкретные замечания и предложения которого в значительной степени способствовали формированию окончательного облика предлагаемой читателю книги.

Авторы также выражают благодарность Антипенко О.А. за качественное выполнение большого объема работ по техническому оформлению рукописи этой книги.

#### Введение

Для достижения поставленных в предисловии целей авторами была принята следующая последовательность изложения материала.

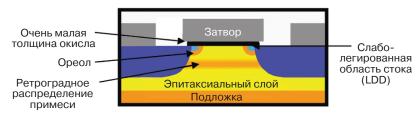

В первой главе изложены теоретические основы работы полевых транзисторов — базовых элементов современных массовых микросхем. Вначале кратко рассмотрены физические основы работы субмикронных транзисторов (типовая структура, область объединения, оценка величины накопленного заряда в слое инверсии, расчет толщины инверсионного слоя). Затем более детально рассмотрены особенности работы классического полевого транзистора с длинным каналом (механизмы влияния подложки, математические выражения для оценки величины допорогового тока и др.). В заключительной части главы приведены результаты качественного анализа основных физических процессов, происходящих в субмикронном транзисторе, в том числе подробно рассмотрены основные физические эффекты, влияющие на величину порогового напряжения транзистора, и методы ограничения эффекта сквозного пробоя, а также эффекты возникновения токов утечки стока МОП-транзистора, обусловленные влиянием его затвора.

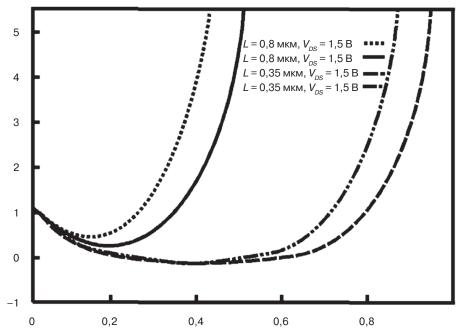

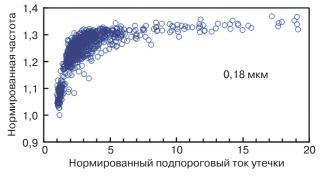

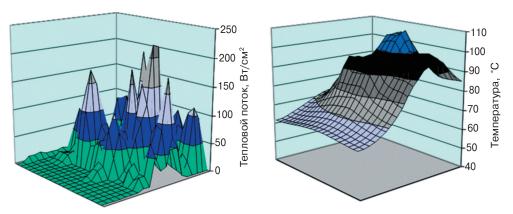

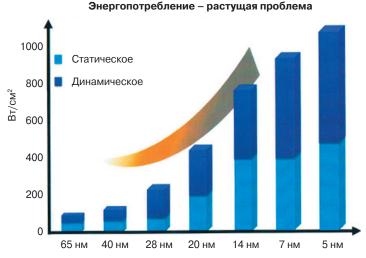

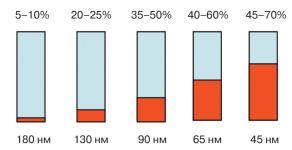

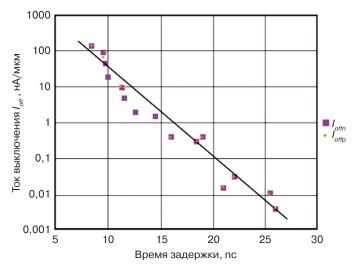

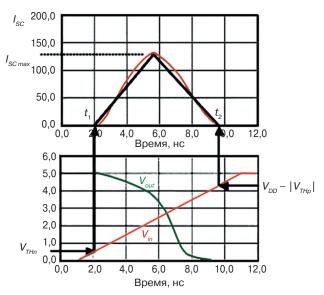

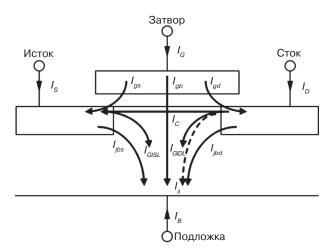

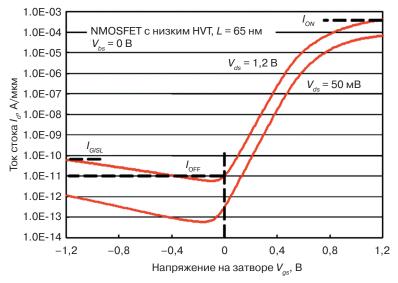

Вторая глава посвящена детальному анализу особенностей конструктивно-схемотехнического проектирования современных субмикронных КМОП-микросхем. Здесь рассматриваются основные проблемы и тенденции развития кремниевых микросхем, пути уменьшения величины энергопотребления микросхем, анализируются физические взаимосвязи между токами утечки и величиной статической мощности, между токами утечки и величиной динамической мощности, а также пути и методы уменьшения суммарной величины потребляемой мощности. Подробно рассмотрены физические причины возникновения этих токов утечки, а именно: подпорогового тока утечки, туннельного тока затвора и тока выключения субмикронного полевого транзистора, а также основные методы уменьшения общей величины потреблений мощности. В отдельном разделе рассмотрены особенности проектирования субмикронных аналоговых и цифро-аналоговых микросхем.